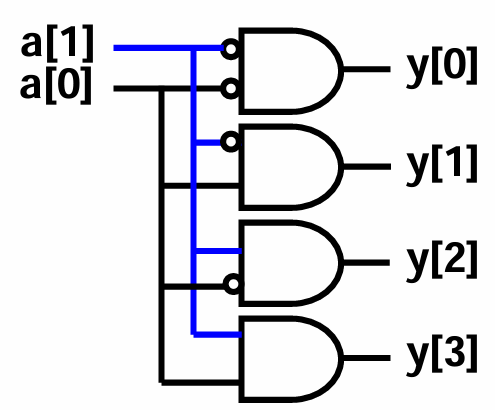

Symbol

사용 코드

|

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

|

module decoder (a, y);

input [1:0] a; // 2비트 입력 신호 a (a[1], a[0])

output [3:0] y; // 4비트 출력 신호 y

wire [3:0] y; // output y와 중복 선언

// 2-to-4 디코더 출력 논리

assign y[0] = !a[1] & !a[0]; // 입력이 00일 때 y[0] = 1

assign y[1] = !a[1] & a[0]; // 입력이 01일 때 y[1] = 1

assign y[2] = a[1] & !a[0]; // 입력이 10일 때 y[2] = 1

assign y[3] = a[1] & a[0]; // 입력이 11일 때 y[3] = 1

endmodule

|

cs |

사용 코드

|

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

|

module decoder (a, y);

input [1:0] a; // 2비트 입력 신호 a (a[1], a[0])

output [3:0] y; // 4비트 출력 신호 y

wire [3:0] y; // output y와 중복 선언

// 입력 값에 따라 해당 y 비트만 1, 나머지는 0

assign y[0] = (a[1:0] == 2'b00); // a = 00 → y[0] = 1

assign y[1] = (a[1:0] == 2'b01); // a = 01 → y[1] = 1

assign y[2] = (a[1:0] == 2'b10); // a = 10 → y[2] = 1

assign y[3] = (a[1:0] == 2'b11); // a = 11 → y[3] = 1

endmodule

|

cs |

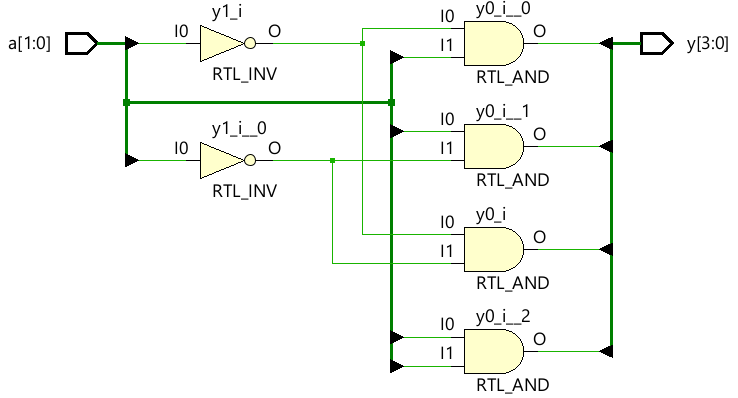

Schenatic

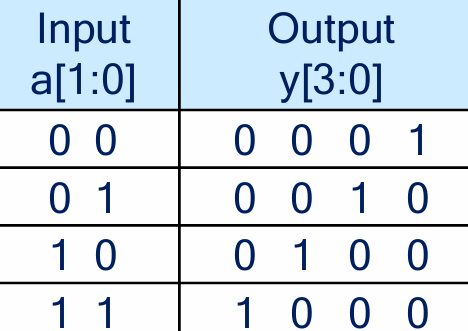

진리표를 보고 코드 작성

사용 코드

|

1

2

3

4

5

6

7

8

9

10

11

12

13

14

|

module de_coder (a, y);

input [1:0] a; // 2비트 입력 신호 (a[1], a[0])

output [3:0] y; // 4비트 출력 신호 y

wire [3:0] y; // ❗ output y와 중복 선언 (Vivado 등 합성기에서 경고/에러 발생 가능)

// 입력 값에 따라 4비트 y 출력 설정 (2-to-4 디코더 동작)

assign y = (a == 2'b00) ? 4'b0001 : // a = 00 → y = 0001

(a == 2'b01) ? 4'b0010 : // a = 01 → y = 0010

(a == 2'b10) ? 4'b0100 : // a = 10 → y = 0100

4'b1000; // a = 11 → y = 1000

endmodule

|

cs |

사용 코드

|

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

|

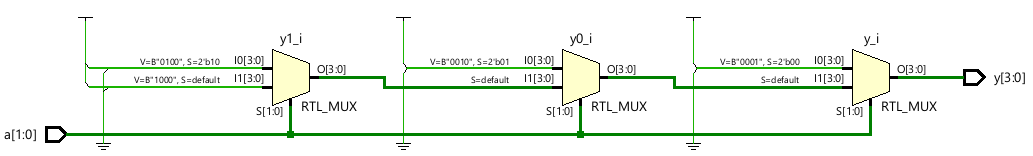

module d_coder (a, y);

input [1:0] a; // 2비트 입력 신호 (a[1], a[0])

output [3:0] y; // 4비트 출력 신호 y

reg [3:0] y; // always 블록에서 y를 할당하므로 reg 타입으로 선언

always @(a) begin // a 값이 바뀔 때마다 실행

case (a)

2'b00 : y = 4'b0001; // a = 00 -> y = 0001

2'b01 : y = 4'b0010; // a = 01 -> y = 0010

2'b10 : y = 4'b0100; // a = 10 -> y = 0100

2'b11 : y = 4'b1000; // a = 11 -> y = 1000

endcase

end

endmodule

|

cs |

Schematic

'Verilog_RTL 설계' 카테고리의 다른 글

| [Verilog_RTL]_4BIT_ALU (0) | 2025.06.14 |

|---|---|

| [Verilog_RTL]_LOGIC_GATE (0) | 2025.06.14 |

| [Verilog]_4BIT_ADDER/SUBTRACTOR (0) | 2025.06.14 |

| [Verilog]_4BIT_ADDER (0) | 2025.06.14 |

| [Verilog]_Tri_state_Buffer / Inverter (0) | 2025.06.14 |