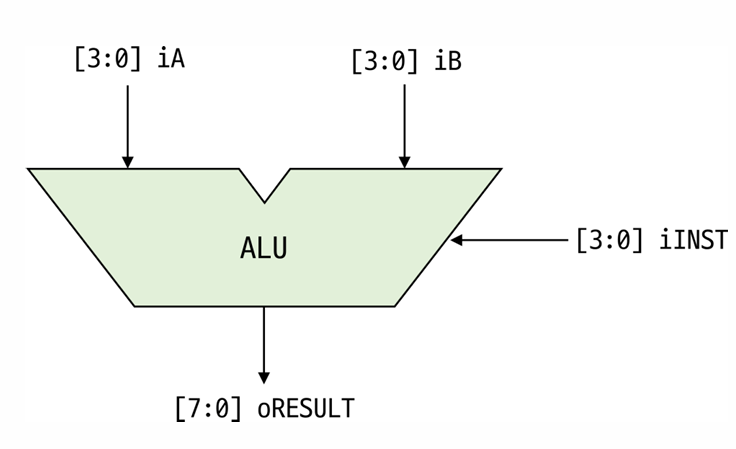

Symbol

사용 코드_case 문

|

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

|

module alu_4bit (iA, iB, ilNST, oRESULT);

// 연산 종류를 나타내는 localparam 상수 (명령어 코드)

localparam ADD = 4'h0, // 덧셈

SUB = 4'h1, // 뺄셈

MUL = 4'h2, // 곱셈

DIV = 4'h3, // 나눗셈

MOD = 4'h4, // 나머지

BIT_NOT = 4'h5, // 비트 반전

BIT_AND = 4'h6, // 비트 AND

BIT_OR = 4'h7, // 비트 OR

BIT_XOR = 4'h8, // 비트 XOR

BIT_XNOR = 4'h9, // 비트 XNOR

RED_AND = 4'ha, // reduction AND

RED_OR = 4'hb, // reduction OR

RED_NAND = 4'hc, // reduction NAND

RED_XOR = 4'hd, // reduction XOR

RSHFT = 4'he, // 우측 시프트

LSHFT = 4'hf; // 좌측 시프트

input [3:0] iA, iB; // 연산에 사용되는 4비트 입력 A, B

input [3:0] ilNST; // 연산 선택 코드

output [7:0] oRESULT; // 8비트 출력 결과

reg [7:0] result; // always 블록에서 연산 결과를 저장 (reg 타입)

always @(iA or iB or ilNST) begin

case (ilNST)

ADD : result = iA + iB; // 덧셈

SUB : result = iA - iB; // 뺄셈

MUL : result = iA * iB; // 곱셈

DIV : result = iA / iB; // 나눗셈

MOD : result = iA % iB; // 나머지 연산

BIT_NOT : result = ~iA; // 비트 반전

BIT_AND : result = iA & iB; // 비트 AND

BIT_OR : result = iA | iB; // 비트 OR

BIT_XOR : result = iA ^ iB; // 비트 XOR

BIT_XNOR : result = iA ~^ iB; // 비트 XNOR

RED_AND : result = &iA; // reduction AND

RED_OR : result = |iA; // reduction OR

RED_NAND : result = ~&iA; // reduction NAND

RED_XOR : result = ^iA; // reduction XOR

RSHFT : result = iA >> iB; // 오른쪽 시프트

LSHFT : result = iA << iB; // 왼쪽 시프트

default : result = 8'h0; // 기본값 (Latch 방지)

endcase

end

assign oRESULT = result; // 연산 결과를 출력에 연결

endmodule

|

cs |

사용 코드_Testbench

|

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

|

module tb_alu;

reg [3:0] iA, iB, iINST; // ALU의 4비트 입력 피연산자 iA, iB 와 4비트 명령어 iINST

wire [7:0] oRESULT; // ALU의 8비트 연산 결과 출력

integer i; // 루프 카운터용 정수형 변수

// ALU 모듈 인스턴스화 (이름에 의한 포트 매핑)

alu U0 (

.iA (iA), // 4비트 입력 iA

.iB (iB), // 4비트 입력 iB

.iINST (iINST), // 4비트 명령어 입력

.oRESULT (oRESULT) // 8비트 결과 출력

);

// 초기 입력 신호 생성 및 테스트 진행

initial begin

iA = 4'hb; // iA = 1011 (16진수 b = 10진수 11)

iB = 4'h2; // iB = 0010 (16진수 2 = 10진수 2)

iINST = 4'h0; // 명령어 초기값: 0000

// iINST를 0부터 15까지 1씩 증가시키며 테스트 (모든 ALU 연산 코드 적용)

for (i = 0; i <= 15; i = i + 1) begin

#100; // 100ns 대기 후

iINST = iINST + 1; // iINST를 1씩 증가 (다음 연산 명령어로 변경)

end

end

endmodule

|

cs |

Schematic

'Verilog_RTL 설계' 카테고리의 다른 글

| [Verilog_RTL]_10-to-2_ENCODER (0) | 2025.06.16 |

|---|---|

| [Verilog_RTL]_Binary_BCD 변환기 (0) | 2025.06.14 |

| [Verilog_RTL]_LOGIC_GATE (0) | 2025.06.14 |

| [Verilog_RTL]_DECODER (0) | 2025.06.14 |

| [Verilog]_4BIT_ADDER/SUBTRACTOR (0) | 2025.06.14 |