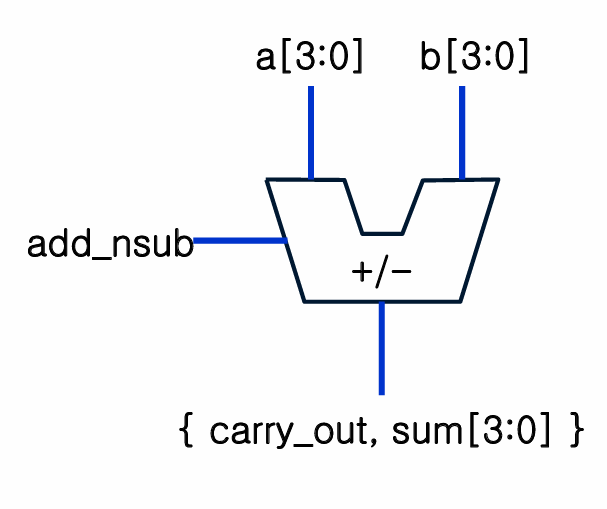

Symbol

사용 코드

|

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

|

module sub_add_4bit (a, b, add_nsub, cout, sum);

input [3:0] a, b; // 4비트 입력: a, b

input add_nsub; // 연산 선택: 1 = 덧셈, 0 = 뺄셈

output cout; // 자리올림 (또는 자리내림) 비트

output [3:0] sum; // 결과 값 (합 or 차)

wire cout; // output cout과 중복 선언

wire [3:0] sum; // output sum과 중복 선언

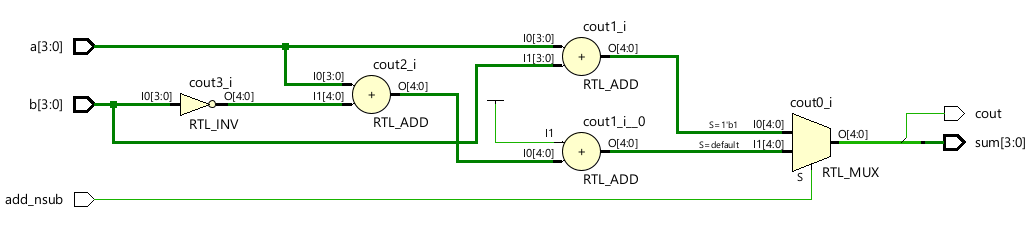

// add_nsub = 1 → a + b

// add_nsub = 0 → a + (~b) + 1 = a - b (2의 보수 뺄셈)

assign {cout, sum[3:0]} =

add_nsub ? (a[3:0] + b[3:0]) : (a[3:0] + ~b[3:0] + 4'b1);

endmodule

|

cs |

Schenatic

'Verilog_RTL 설계' 카테고리의 다른 글

| [Verilog_RTL]_LOGIC_GATE (0) | 2025.06.14 |

|---|---|

| [Verilog_RTL]_DECODER (0) | 2025.06.14 |

| [Verilog]_4BIT_ADDER (0) | 2025.06.14 |

| [Verilog]_Tri_state_Buffer / Inverter (0) | 2025.06.14 |

| [Verilog_RTL]_4BIT_MUX (0) | 2025.06.14 |