Symbol

사용 코드

|

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

|

module bcd_bi (iBIN, oBCD);

input [7:0] iBIN; // 8비트 이진 입력

output [11:0] oBCD; // 12비트 BCD 출력 (3자리 BCD)

reg [11:0] bcd; // 변환 중간값 및 최종 BCD 값 저장

integer i; // 반복문 인덱스

assign oBCD = bcd; // 내부 bcd 값을 출력 oBCD에 연결

// Double-Dabble (Shift-and-Add-3) 알고리즘

always @(iBIN) begin

bcd = 12'b0; // BCD 값 초기화

// 8비트 입력을 순차적으로 변환

for (i = 0; i < 8; i = i + 1) begin

// 각 자리 BCD 값이 5 이상이면 +3

if (bcd[3:0] >= 5)

bcd[3:0] = bcd[3:0] + 3;

else

bcd[3:0] = bcd[3:0]; // 필요 없는 else (변화 없음)

if (bcd[7:4] >= 5)

bcd[7:4] = bcd[7:4] + 3;

else

bcd[7:4] = bcd[7:4]; // 필요 없는 else

if (bcd[11:8] >= 5)

bcd[11:8] = bcd[11:8] + 3;

else

bcd[11:8] = bcd[11:8]; // 필요 없는 else

// 좌측으로 쉬프트하며 이진 입력의 비트를 추가

bcd = {bcd[10:0], iBIN[7 - i]};

end

end

endmodule

|

cs |

Schematic

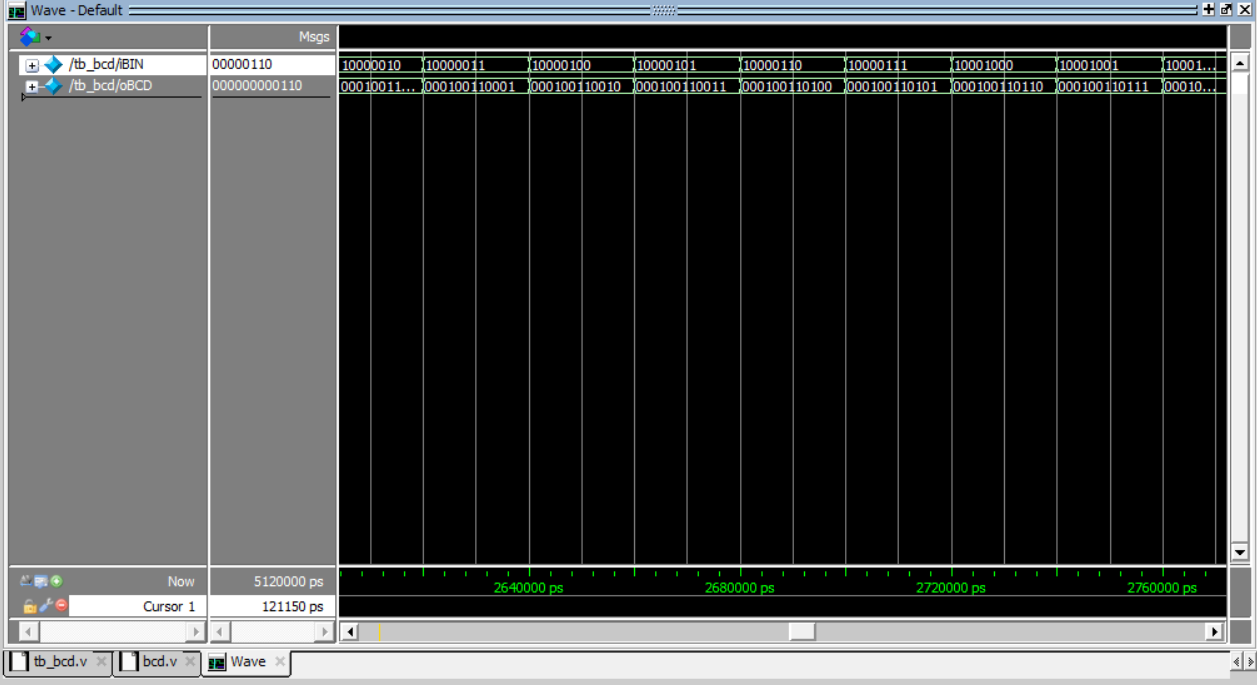

Simulation

'Verilog_RTL 설계' 카테고리의 다른 글

| [Verilog_RTL]_2-to-10_DECODER (0) | 2025.06.16 |

|---|---|

| [Verilog_RTL]_10-to-2_ENCODER (0) | 2025.06.16 |

| [Verilog_RTL]_4BIT_ALU (0) | 2025.06.14 |

| [Verilog_RTL]_LOGIC_GATE (0) | 2025.06.14 |

| [Verilog_RTL]_DECODER (0) | 2025.06.14 |