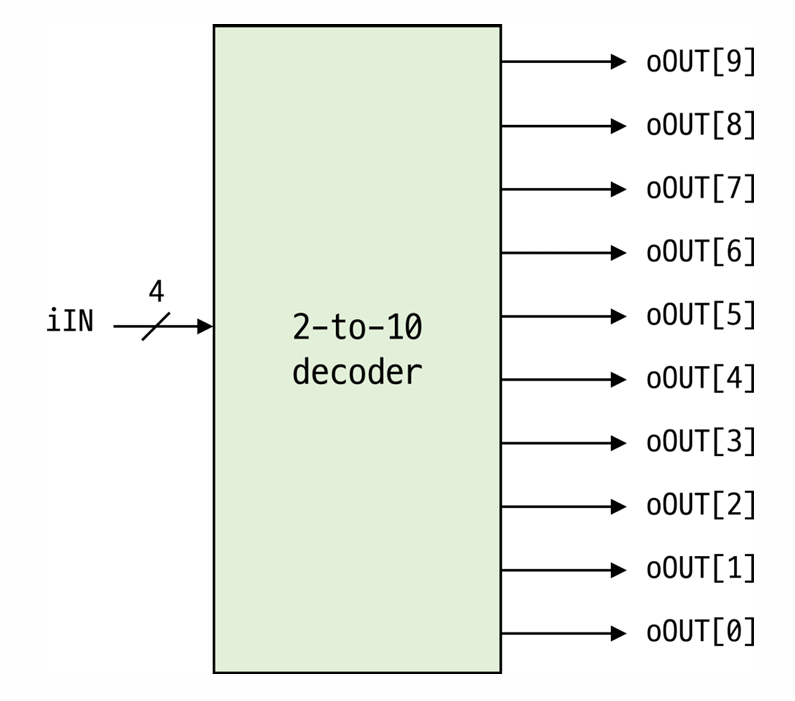

Symbol

사용 코드_case 문

|

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

|

module decoder (iIN, oOUT);

input [3:0] iIN; // 4비트 입력: 0~9 (디코더 입력)

output [9:0] oOUT; // 10비트 출력: 1-hot 형태의 키패드 출력

reg [9:0] out; // always 블록 내부에서 값을 설정할 레지스터형 출력

// 입력 iIN 값이 변할 때마다 out 값을 갱신

always @(iIN) begin

case (iIN)

0 : out = 10'b00_0000_0001; // 입력 0 -> 출력 0번 비트 high

1 : out = 10'b00_0000_0010; // 입력 1 -> 출력 1번 비트 high

2 : out = 10'b00_0000_0100; // 입력 2 -> 출력 2번 비트 high

3 : out = 10'b00_0000_1000; // 입력 3 -> 출력 3번 비트 high

4 : out = 10'b00_0001_0000; // 입력 4 -> 출력 4번 비트 high

5 : out = 10'b00_0010_0000; // 입력 5 -> 출력 5번 비트 high

6 : out = 10'b00_0100_0000; // 입력 6 -> 출력 6번 비트 high

7 : out = 10'b00_1000_0000; // 입력 7 -> 출력 7번 비트 high

8 : out = 10'b01_0000_0000; // 입력 8 -> 출력 8번 비트 high

9 : out = 10'b10_0000_0000; // 입력 9 -> 출력 9번 비트 high

default : out = 10'b11_1111_1111; // 0~9 외 입력 -> 모든 비트 high (에러 또는 경고)

endcase

end

// out 값을 oOUT에 연결

assign oOUT = out;

endmodule

|

cs |

사용 코드_Testbench

|

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

|

`timescale 1ns / 10ps // 시뮬레이션 시간 단위와 정밀도 설정: 단위 1ns, 정밀도 10ps

module tb_decoder;

reg [3:0] iIN; // 4비트 입력: 디코더 입력 값을 시뮬레이션하기 위한 레지스터

wire [9:0] oOUT; // 10비트 출력: 디코더의 출력 관찰용

integer i; // 루프용 변수

// decoder 모듈 인스턴스화 (디코더 DUT)

deco U0 (

.iIN (iIN), // tb_deco의 iIN을 deco 모듈의 iIN에 연결

.oOUT (oOUT) // deco 모듈의 oOUT을 tb_deco의 oOUT에 연결

);

// 초기 블록: 시뮬레이션 시작 시 한 번 실행

initial begin

iIN = 0; // 초기 입력 값 0 설정

// 0부터 10까지 i를 변화시키며, iIN 값을 증가

for (i = 0; i <= 10; i = i + 1) begin

#100 iIN = iIN + 1; // 100ns마다 iIN을 1씩 증가시켜 디코더 입력 변경

end

end

endmodule

|

cs |

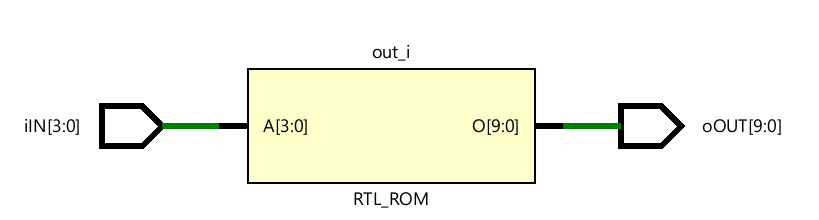

Schematic

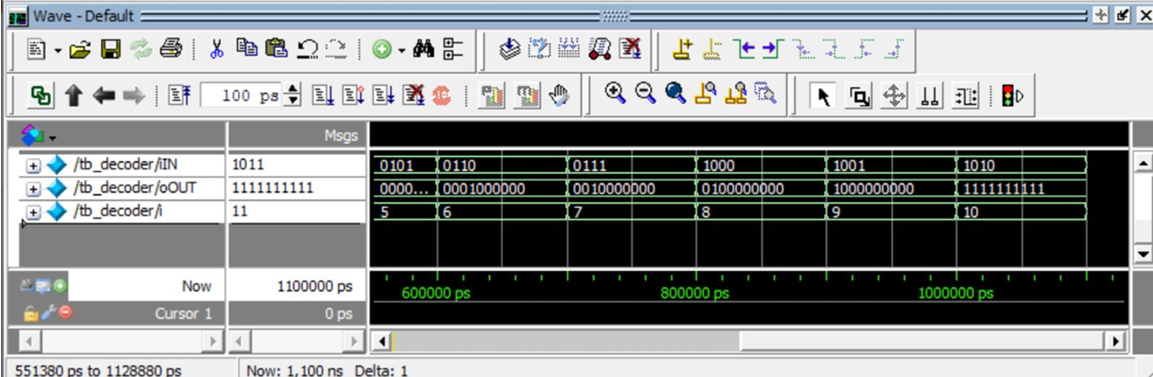

Simultaion

'Verilog_RTL 설계' 카테고리의 다른 글

| [Verilog_RTL]_FSM_moore (0) | 2025.06.20 |

|---|---|

| [Verilog_RTL]_7-Seg_DECODER (0) | 2025.06.20 |

| [Verilog_RTL]_10-to-2_ENCODER (0) | 2025.06.16 |

| [Verilog_RTL]_Binary_BCD 변환기 (0) | 2025.06.14 |

| [Verilog_RTL]_4BIT_ALU (0) | 2025.06.14 |