Symbol

사용 코드_ assign 사용

|

1

2

3

4

5

6

7

8

9

10

11

12

|

module Full_adder (a, b, sel, out);

input a, b; // 입력: a, b (2개의 입력 비트)

input sel; // 선택 신호 (sel이 1이면 a 선택, 0이면 b 선택)

output out; // 출력 신호

wire out; // 출력 포트를 wire로 선언 (※ output은 기본적으로 wire이므로 이 줄은 중복임)

assign out = (sel == 1) ? a : b; // 조건 연산자 사용: sel이 1이면 a를 out에 출력, 아니면 b를 출력 (2:1 MUX 동작)

endmodule

|

cs |

사용 코드_ always 사용

|

1

2

3

4

5

6

7

8

9

10

11

12

13

14

|

module Full_adder (a, b, sel, out);

input a, b; // 입력: a, b (2개의 입력 비트)

input sel; // 선택 신호 (sel이 1이면 a 선택, 0이면 b 선택)

output out; // 출력 포트 선언

reg out; // 출력 신호 out은 always 블록에서 할당되므로 reg 타입으로 선언

always @(sel or a or b) // sel, a, b 중 하나라도 바뀌면 always 블록 실행

out = sel ? a : b; // sel이 1이면 a 출력, 아니면 b 출력 (2:1 MUX 동작)

endmodule

|

cs |

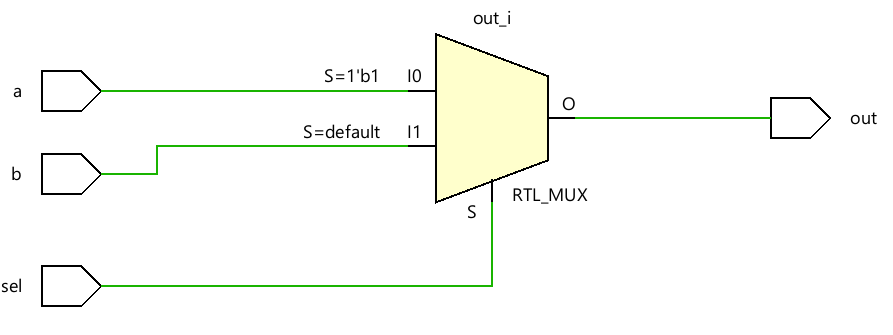

Schematic

'Verilog_RTL 설계' 카테고리의 다른 글

| [Verilog]_Tri_state_Buffer / Inverter (0) | 2025.06.14 |

|---|---|

| [Verilog_RTL]_4BIT_MUX (0) | 2025.06.14 |

| [Verilog_RTL]_FULL_ADDER_GATE (0) | 2025.06.14 |

| [Verilog_RTL]_HALF_ADDER_GATE (0) | 2025.06.13 |

| [Verilog_RTL]_NOR_GATE (0) | 2025.06.13 |