Schematic

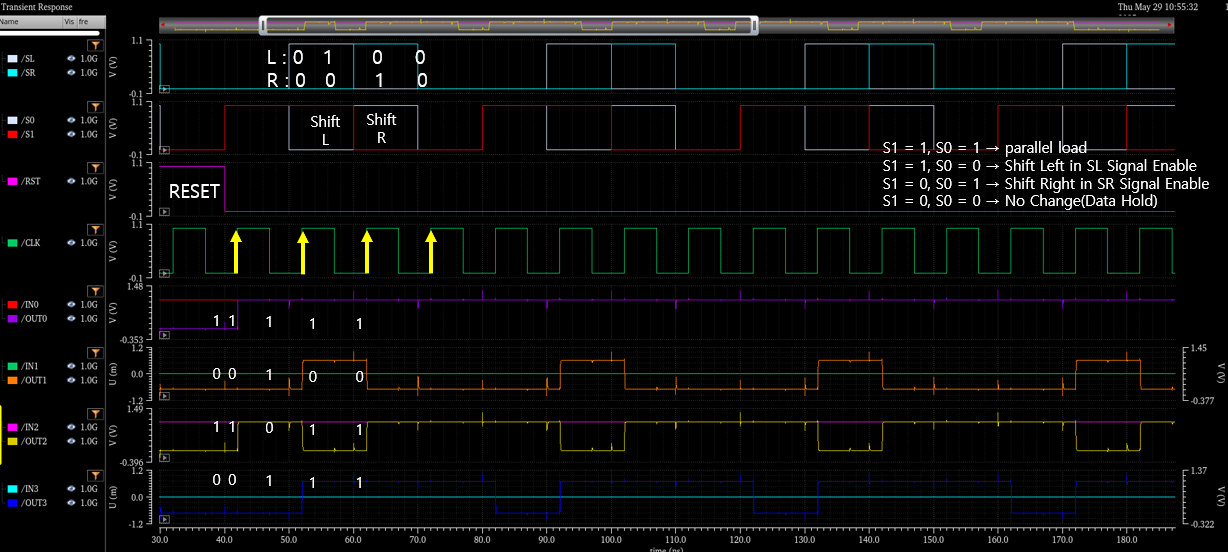

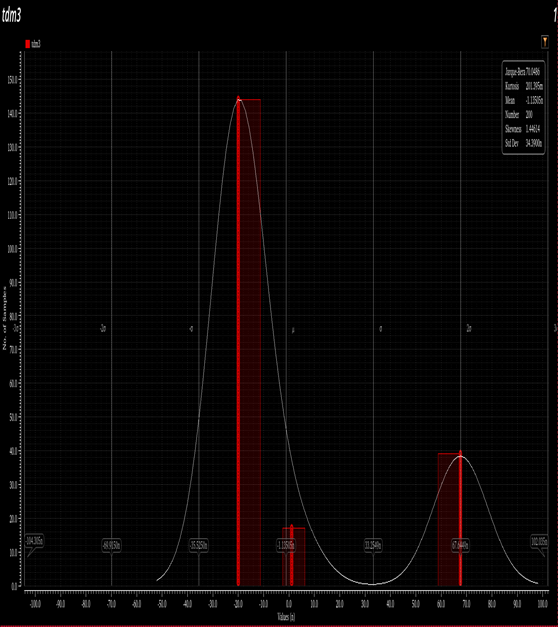

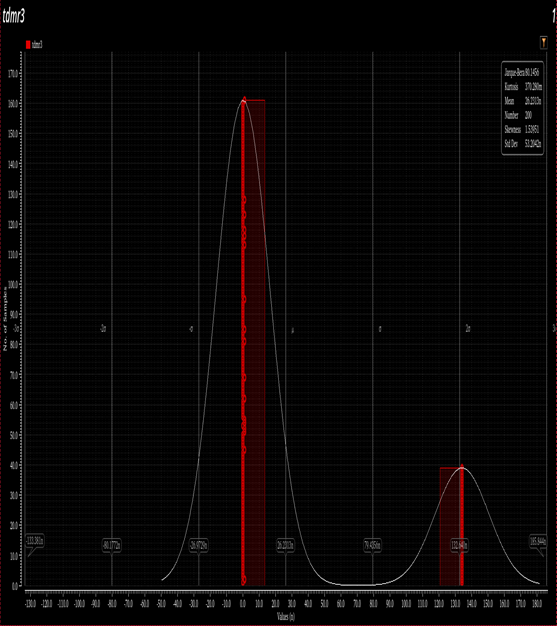

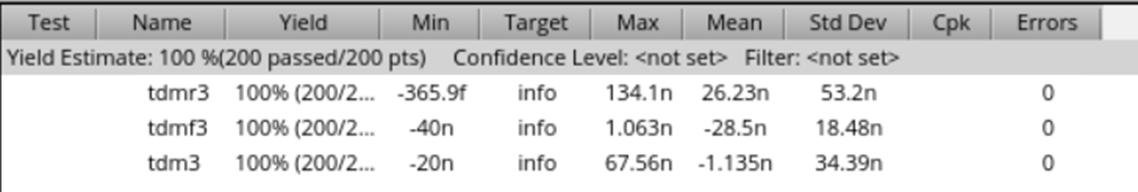

Simualtion

- 그래프를 보면, 약 7GHz까지는 주파수가 증가함에 따라 Delay가 점차 감소하는 경향을 보입니다.

Layout

- Layout size : 가로 52.45 µm

세로 10.81 µm

10.81 * 52.45 = 566.984 µm^2

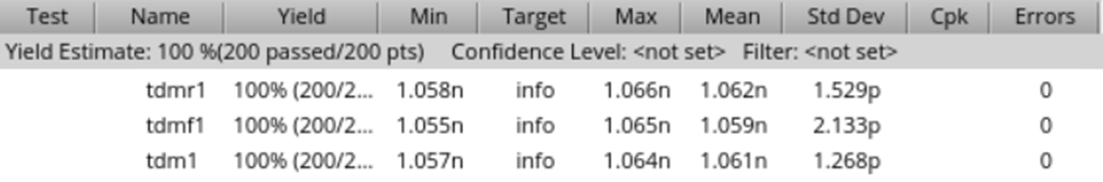

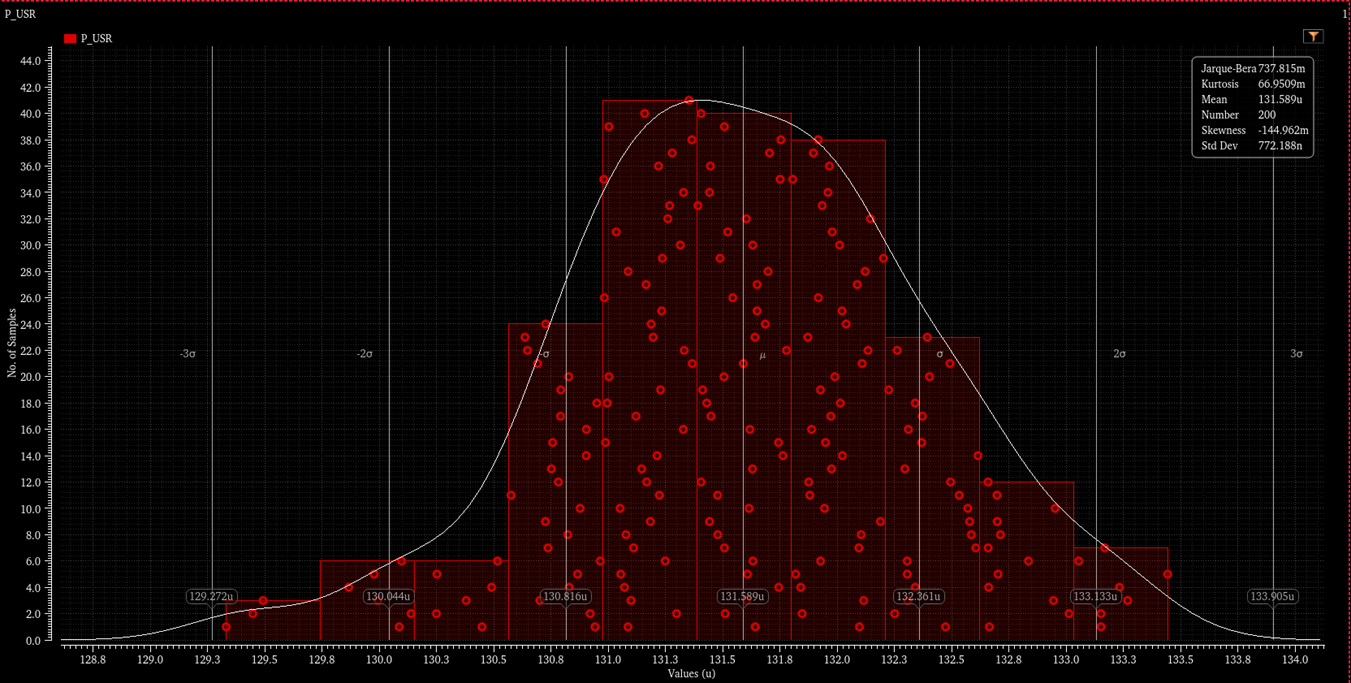

결론

| Transmission Gate - DFF |

NAND DFF |

|

| #TR | 24 | 34 |

| Power(uW) | 51.8708 | 52.9955 |

| Delay(ns) | 1.04094 | 1.09122 |

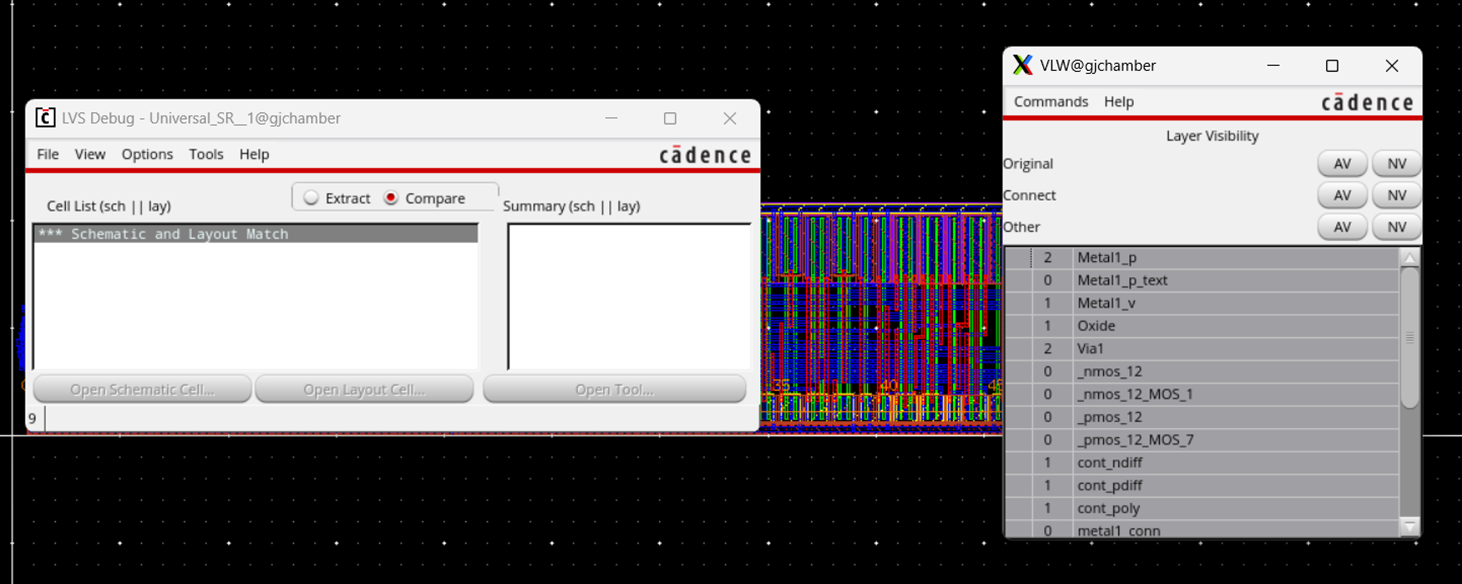

DRC

LVS

'Custom IC one-chip 설계 > DIGITAL LOGIC GATE' 카테고리의 다른 글

| [Digital Logic Gate]_ONE_CHIP (0) | 2025.06.06 |

|---|---|

| [Digital Logic Gate]_TRANSMISSION_D-FF (0) | 2025.06.06 |

| [Digital Logic Gate]_TRANSMISSION_D-FF VS NAND_D-F (3) | 2025.06.06 |

| [Digital Logic Gate]_4BIT_ADDER_SUBTRACTOR (0) | 2025.06.04 |

| [Digital Logic Gate]_4BIT_ADDER (0) | 2025.06.04 |