Place and Route

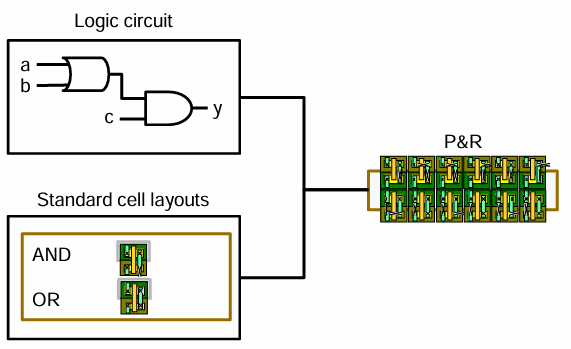

P&R (Place and Route)

• Standard cell 을 이용하여 배치와 연결 진행

•전원망구성 → 클록 트리 합성 → 신호 배선

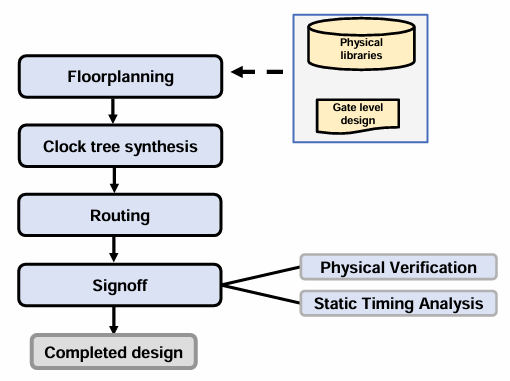

Design Flow

• Floor planning : 다이 / 코어 크기 결정

• CTS : 스큐 / 지연목표에 맞춰 CLK 연결

• Routing : 글로벌 / 디테일 배선, DRC 수정

• Signoff : 물리 검증 후 GDSII 추출

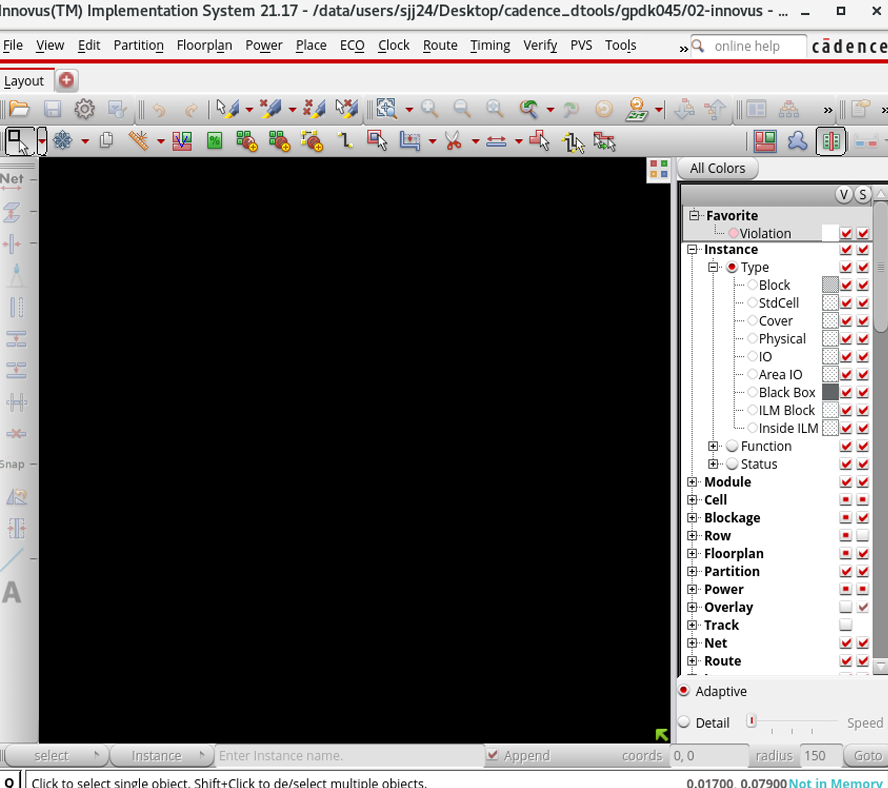

P&R: Innovus 실행

Innovus실행

• 터미널 →cd .. →mkdir

• 실행위치: pwm_design 2innovus 입력 /2innovus

• Digital tool sourcing : souce ../.env_csh_innovus_genus

• 터미널 HiCSL →innovus 입력

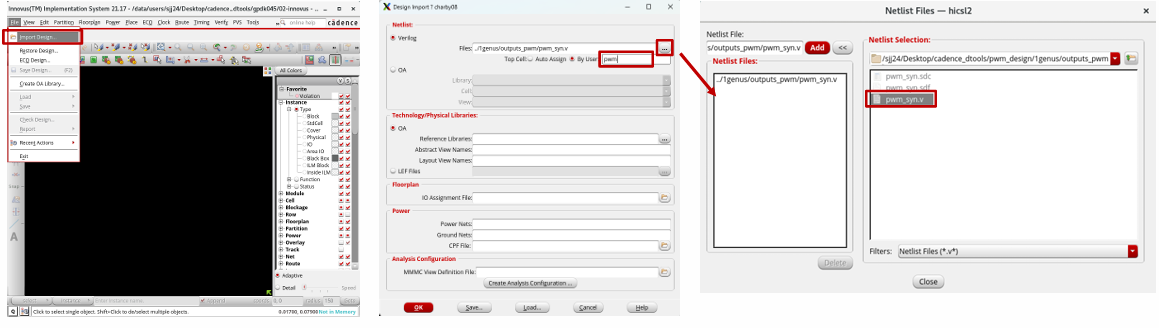

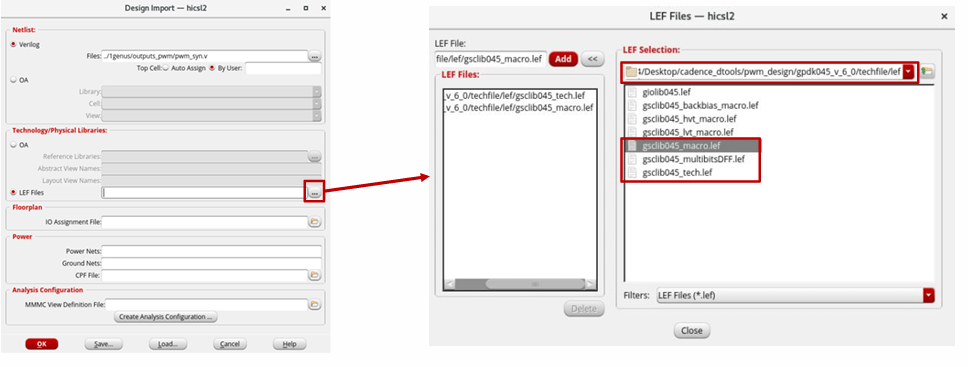

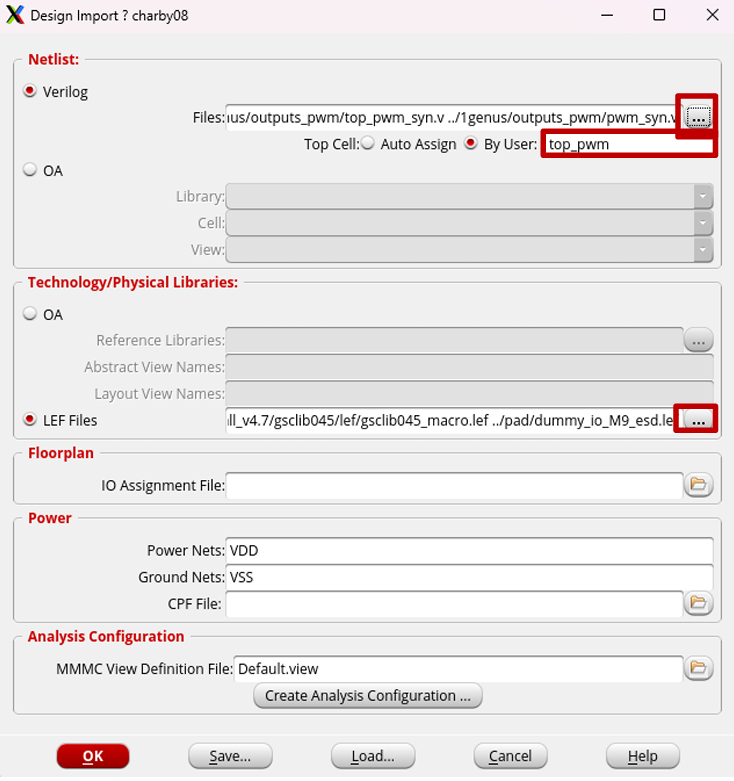

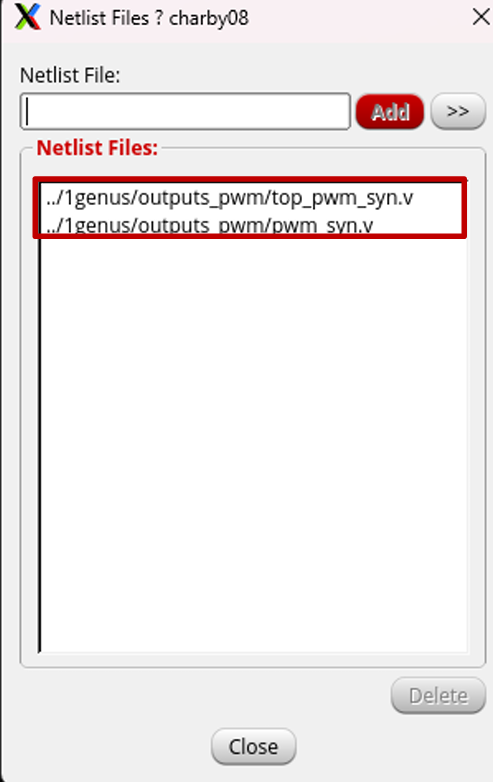

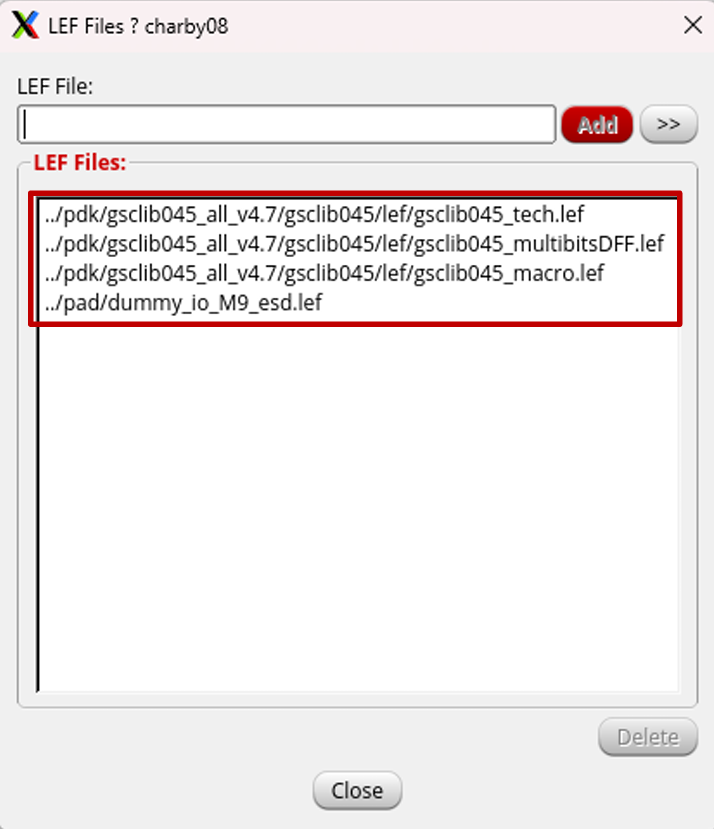

P&R: Import Synthesis File

Technology/Physical Libraries

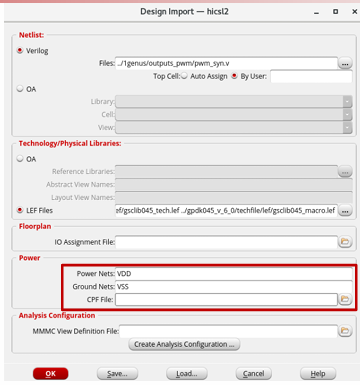

P&R: Power Assign

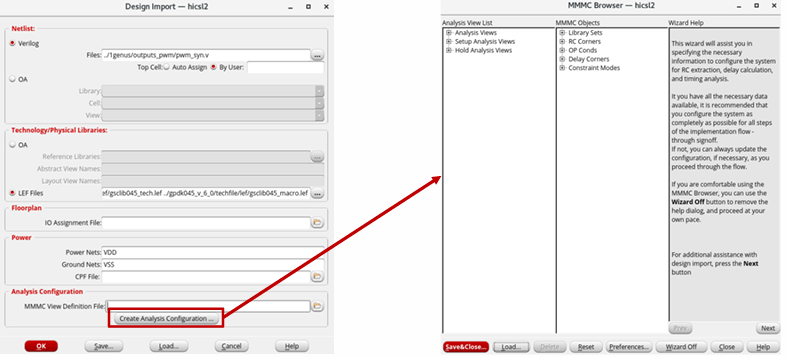

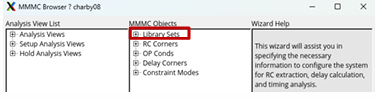

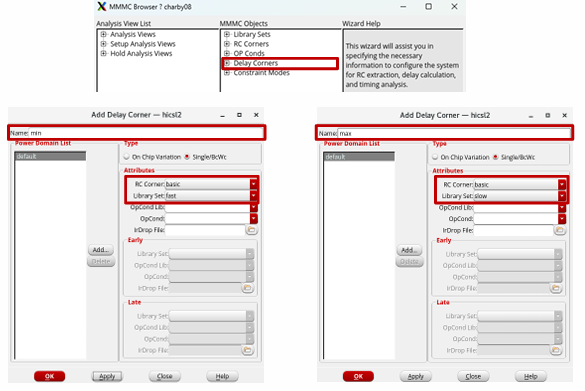

P&R: MMMC(Multi-Mode Multi-Corner) Setup

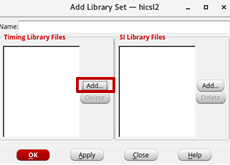

Timing Library Files

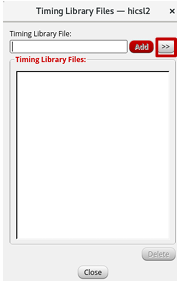

RC Corner

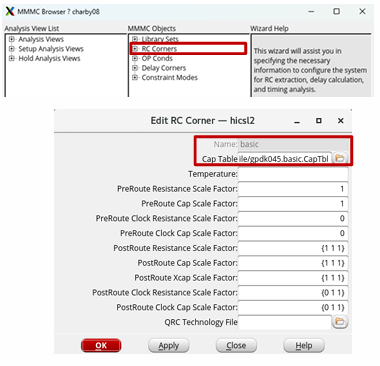

Delay Corner

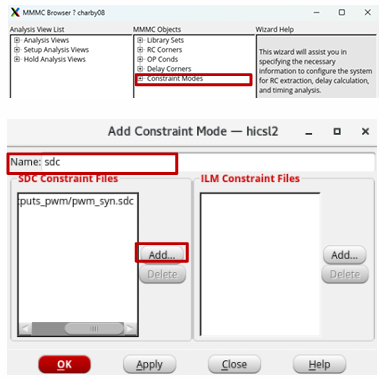

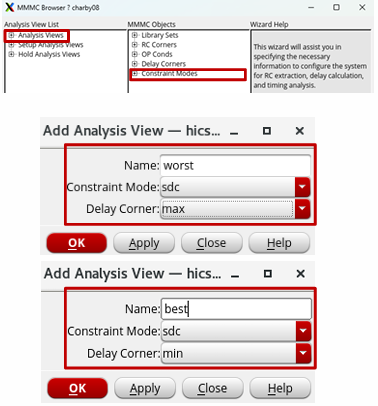

Constraint Modes

Analysis View

설정완료

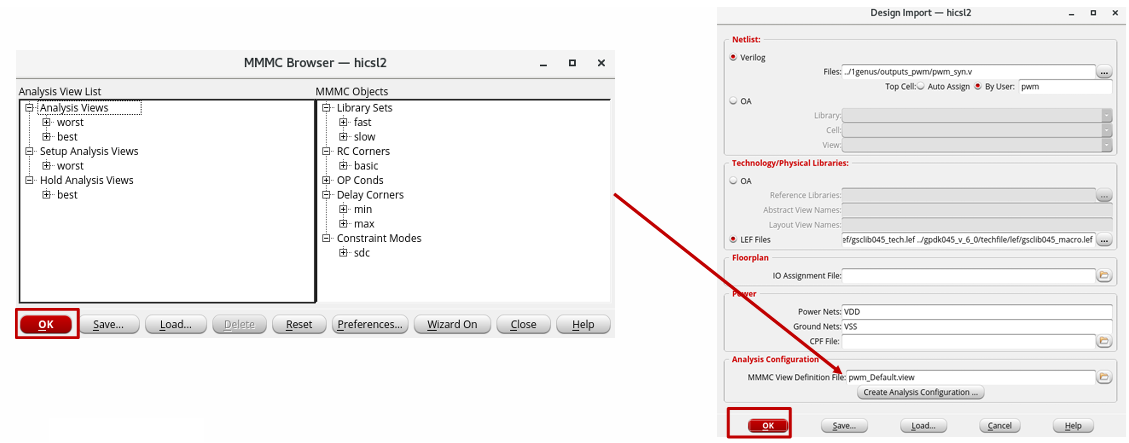

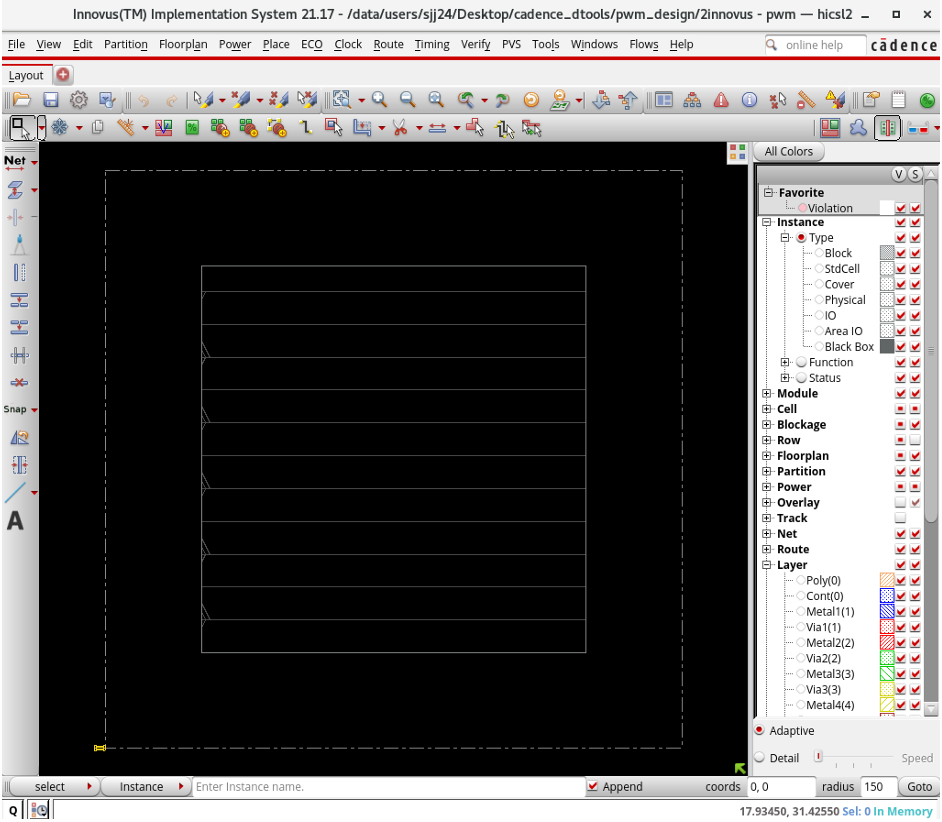

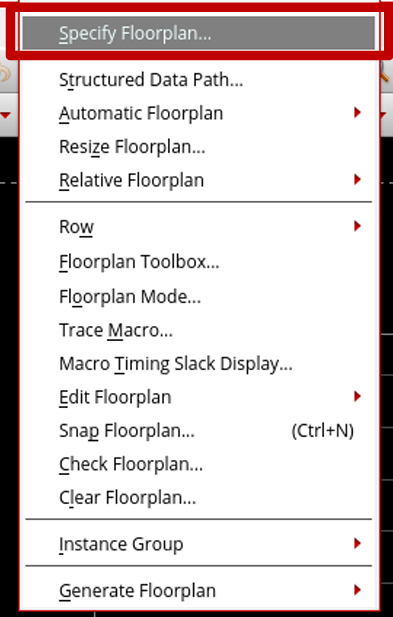

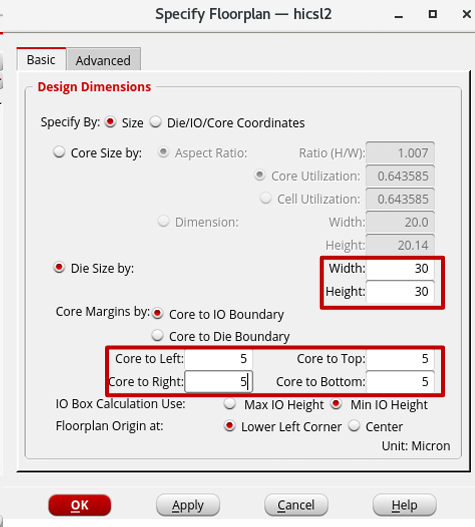

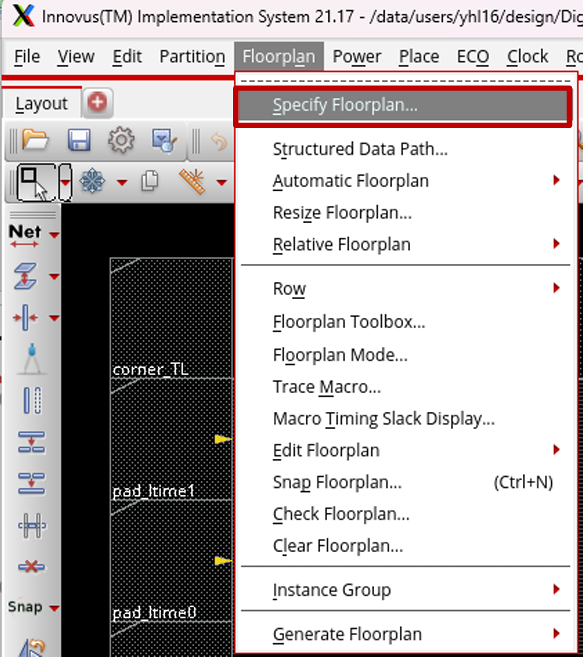

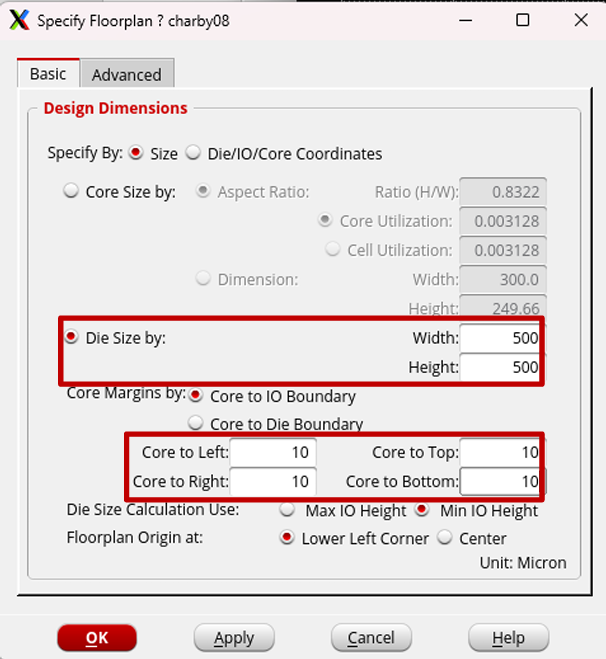

P&R: Specify Floorplan

Floorplan

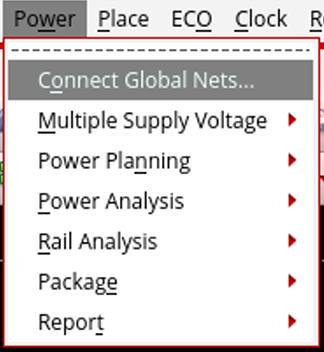

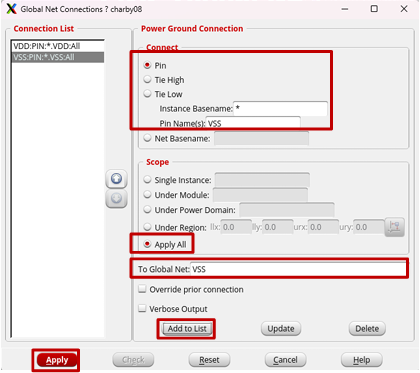

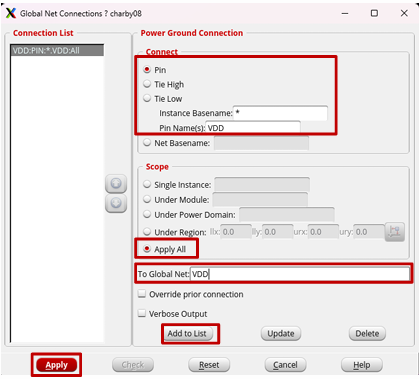

Global Nets

Global VDD,VSS 설정

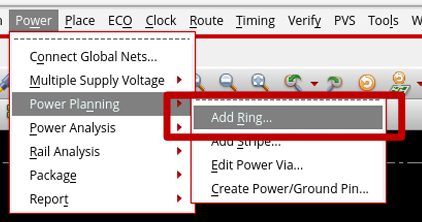

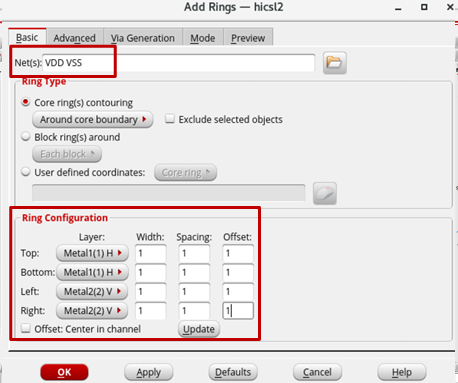

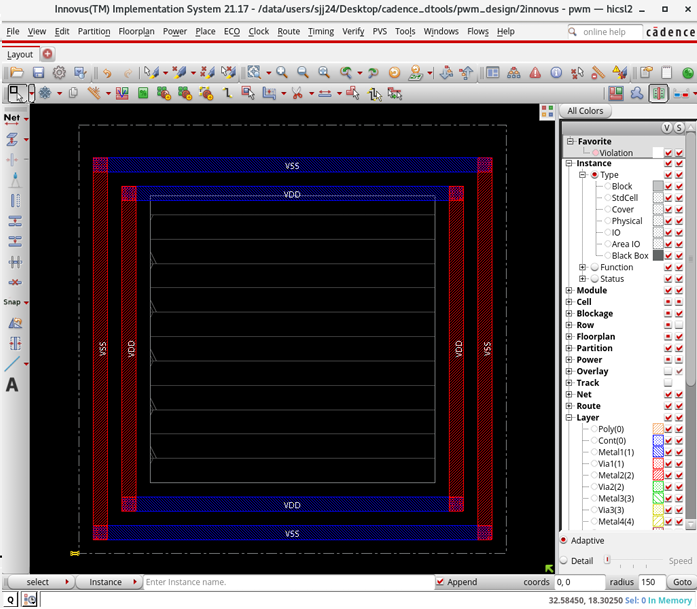

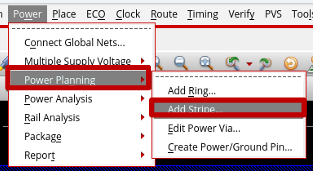

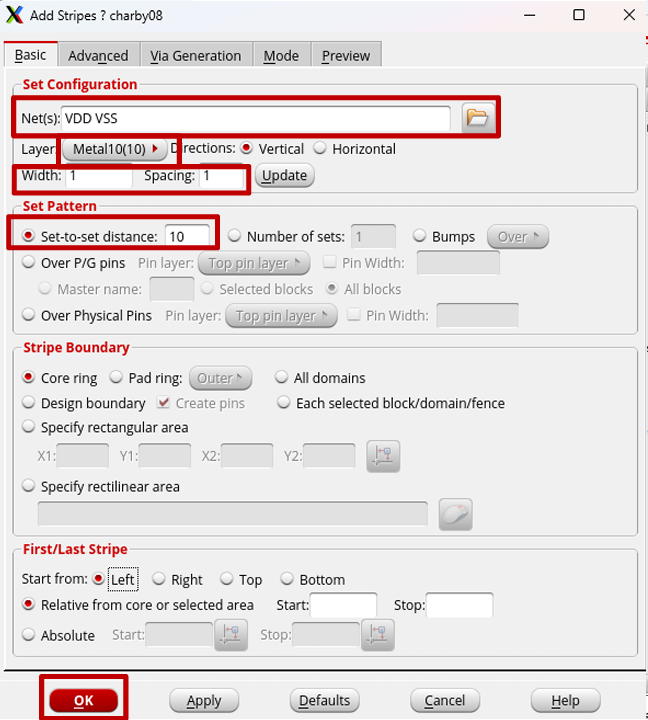

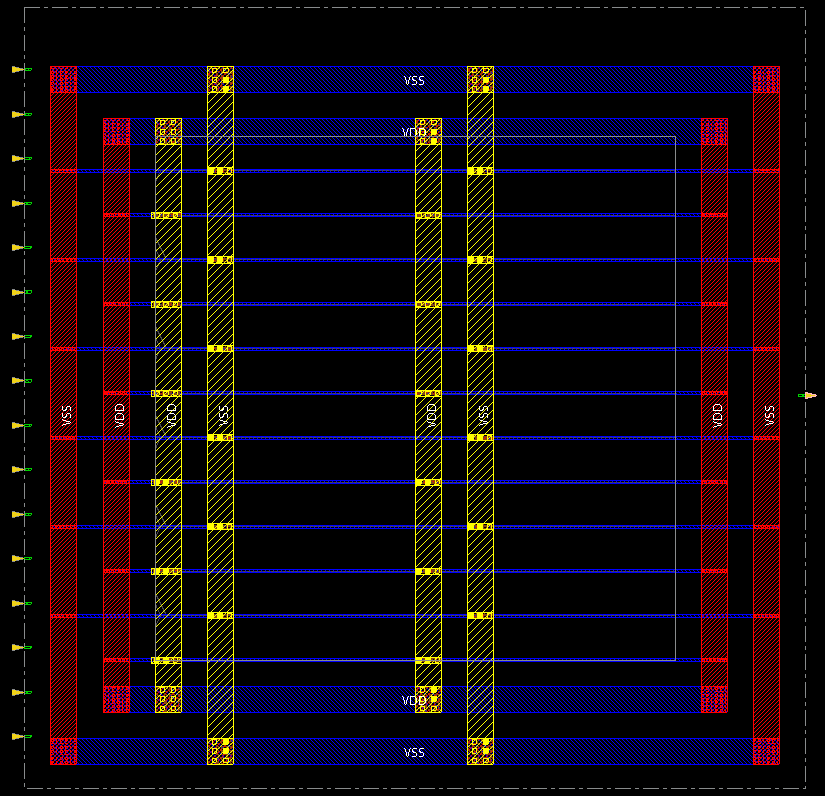

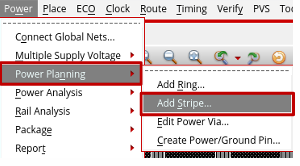

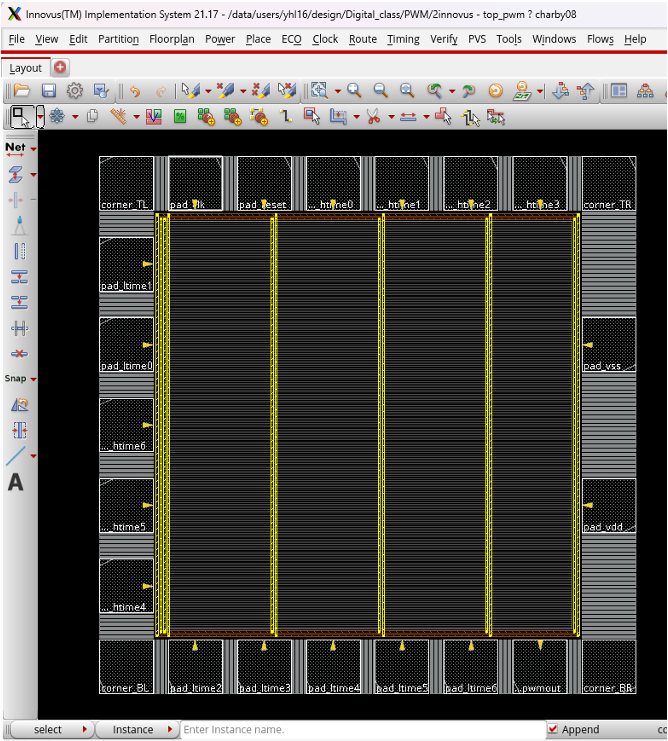

P&R: Add Power Line

Power Ring 추가

Ring configuration: width = 1 , spacing = 1 , offset = 1 (사용한공정drcrule에맞춰서설정)

Power Stripe 추가

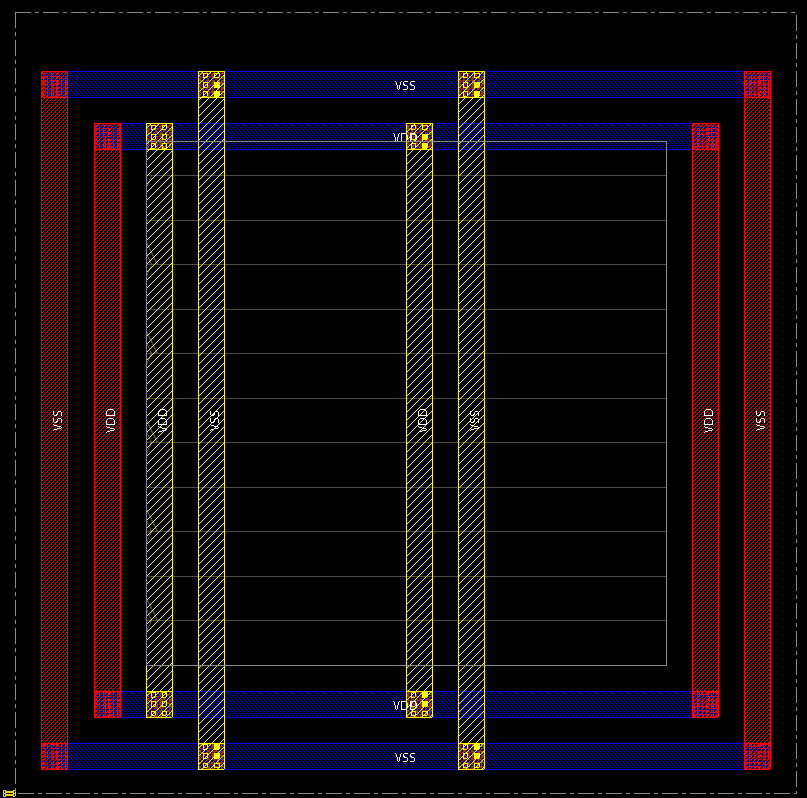

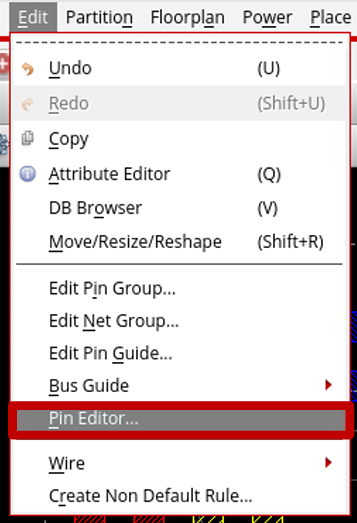

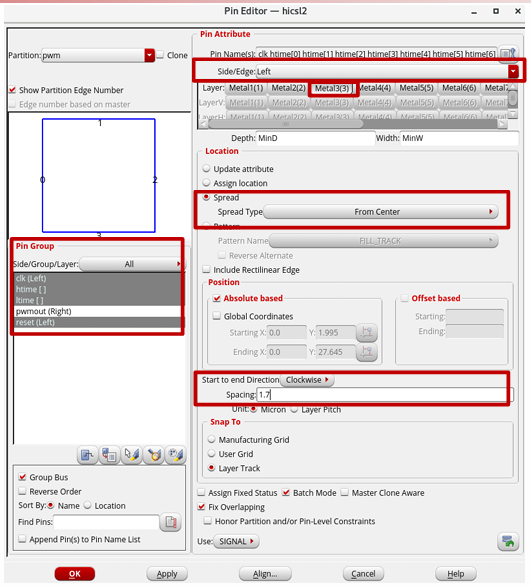

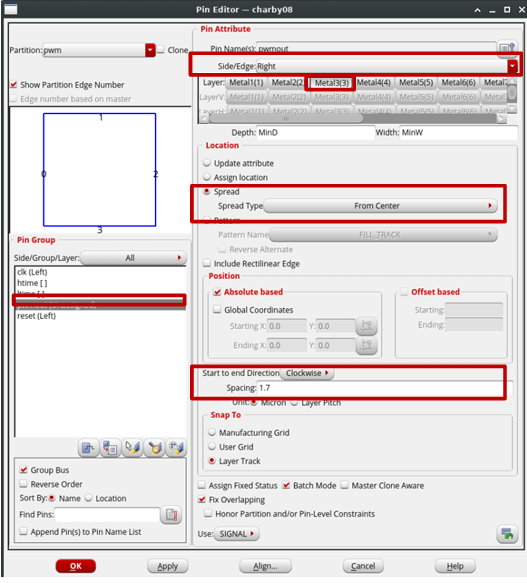

Edit Pin

InputPin 설정

OutputPin 설정

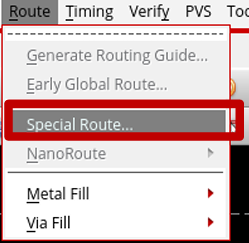

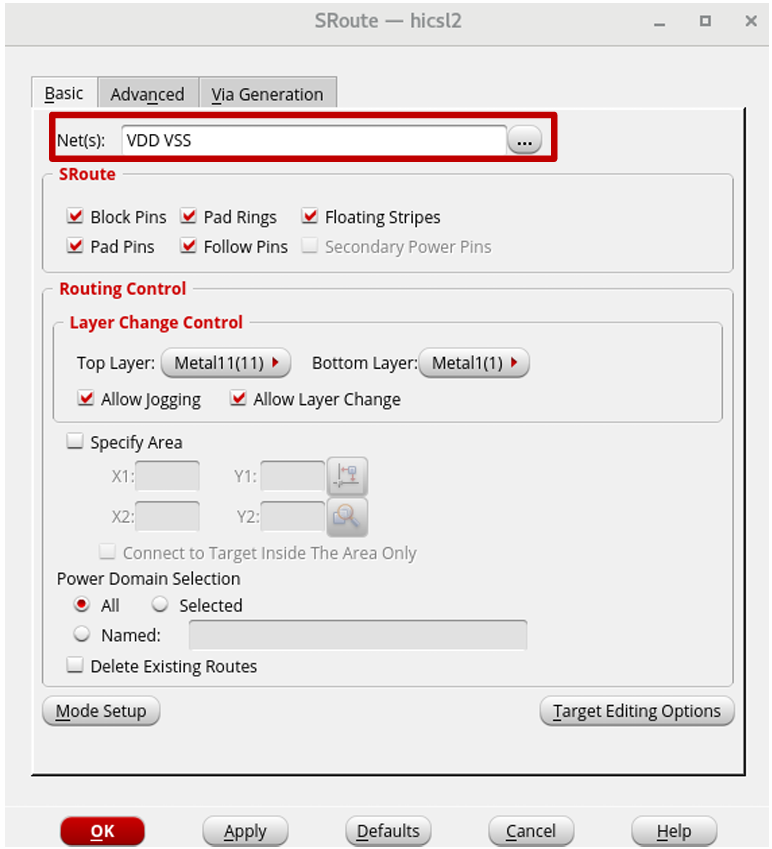

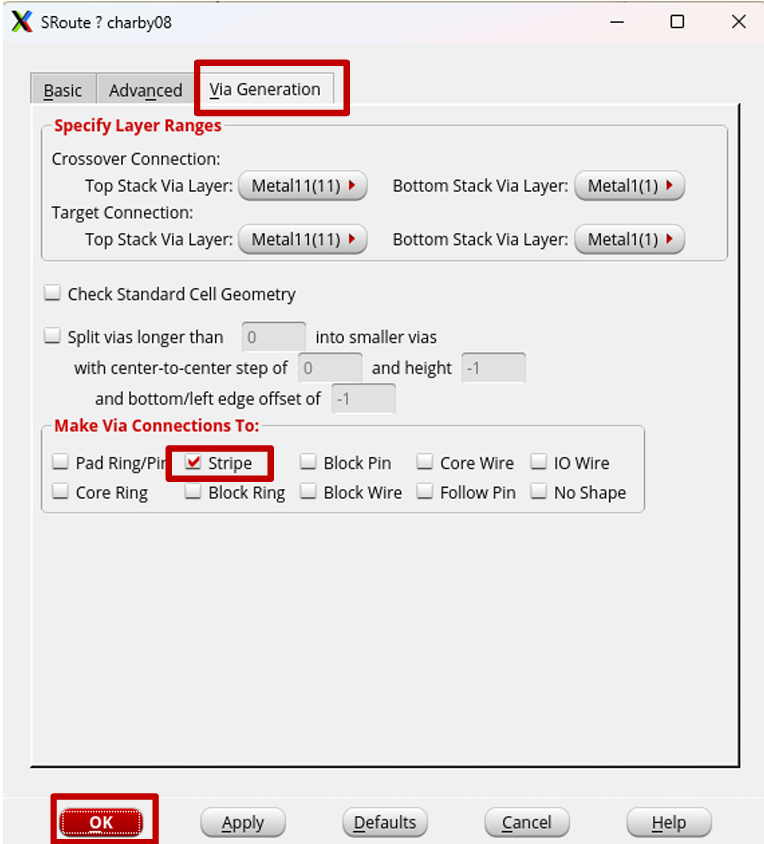

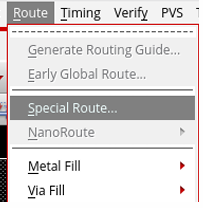

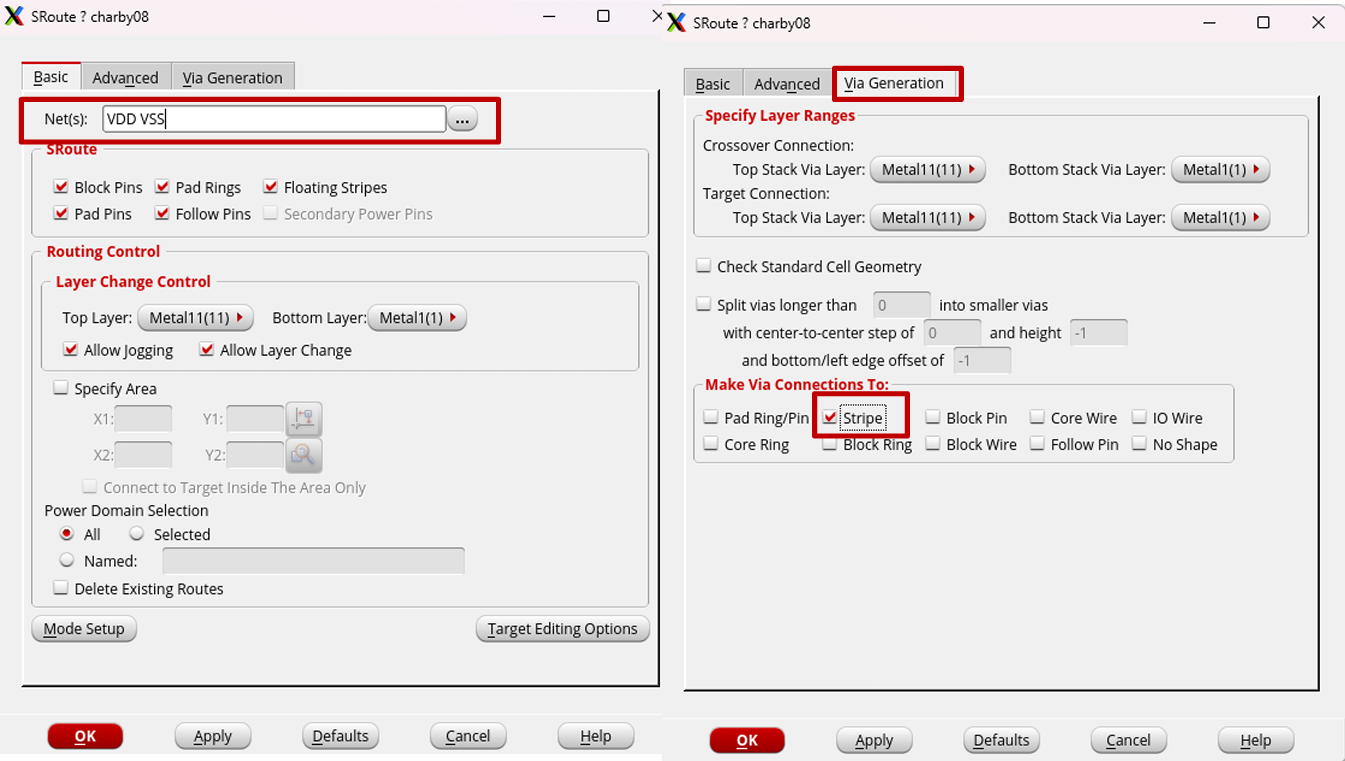

P&R: Special Route

Cell 을위한Power Line 추가

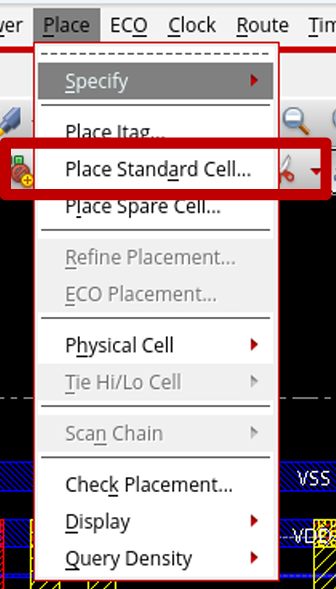

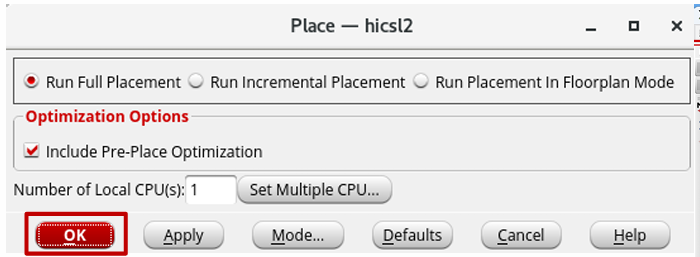

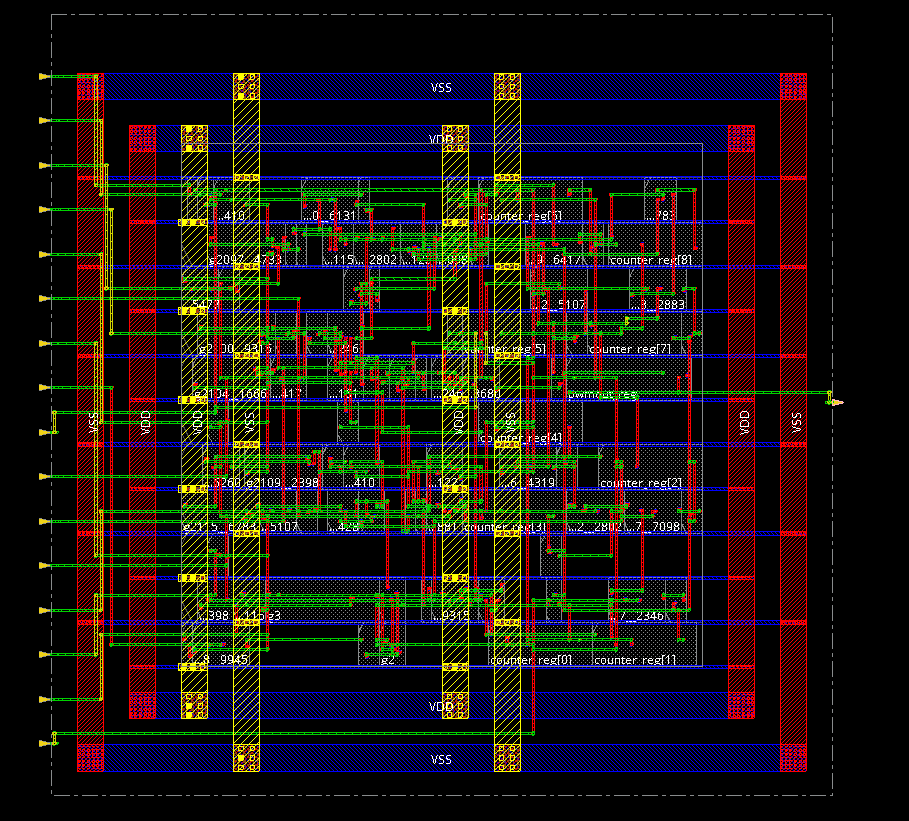

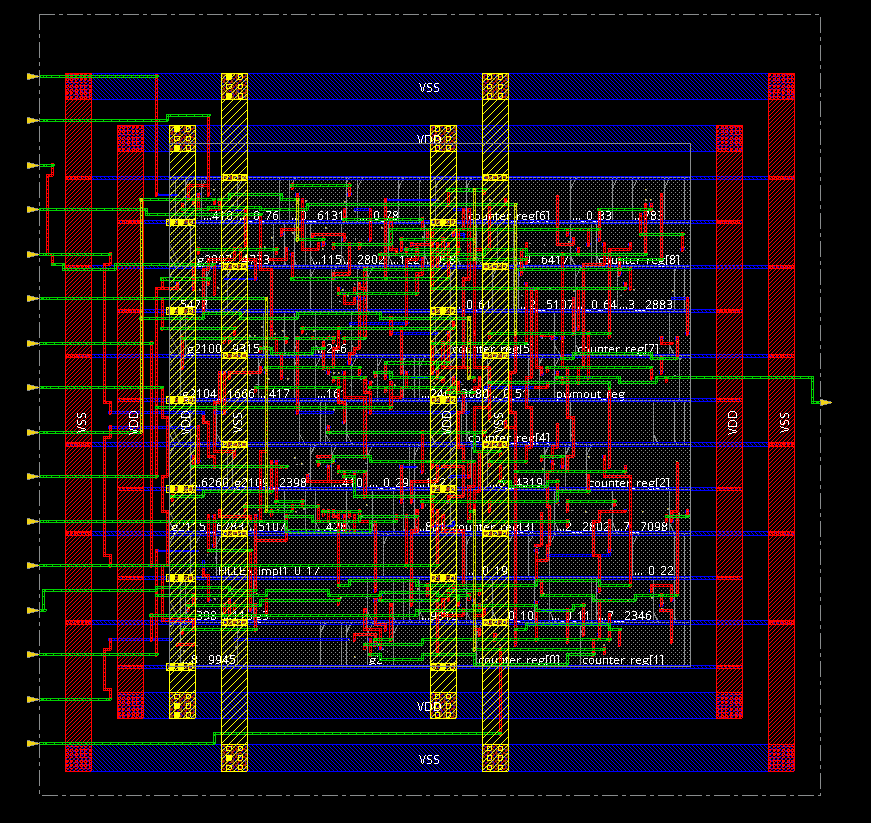

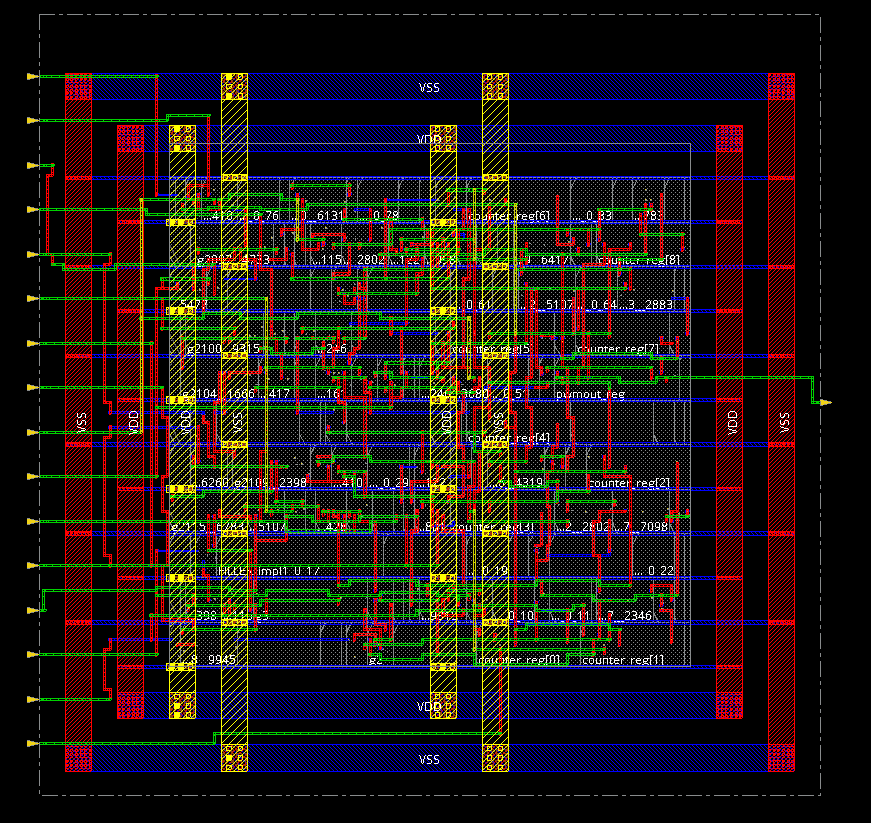

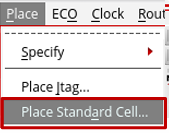

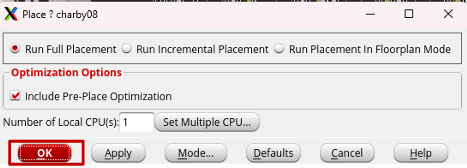

P&R: Place Standard Cells

Standard Cell 배치

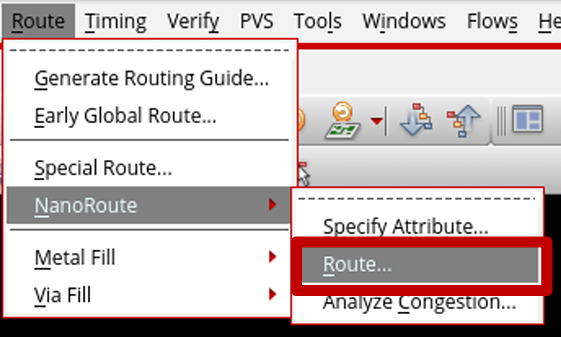

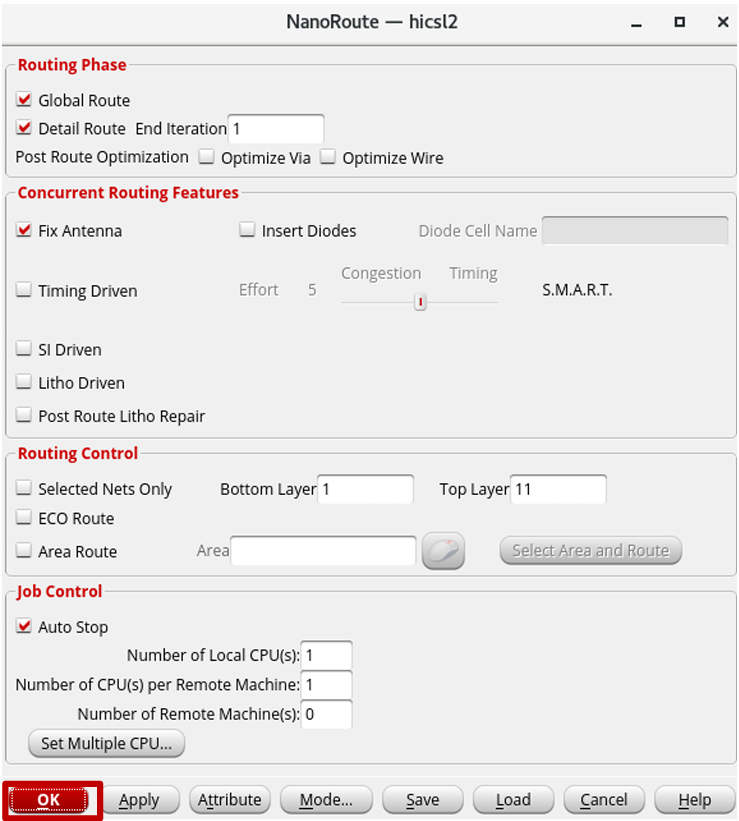

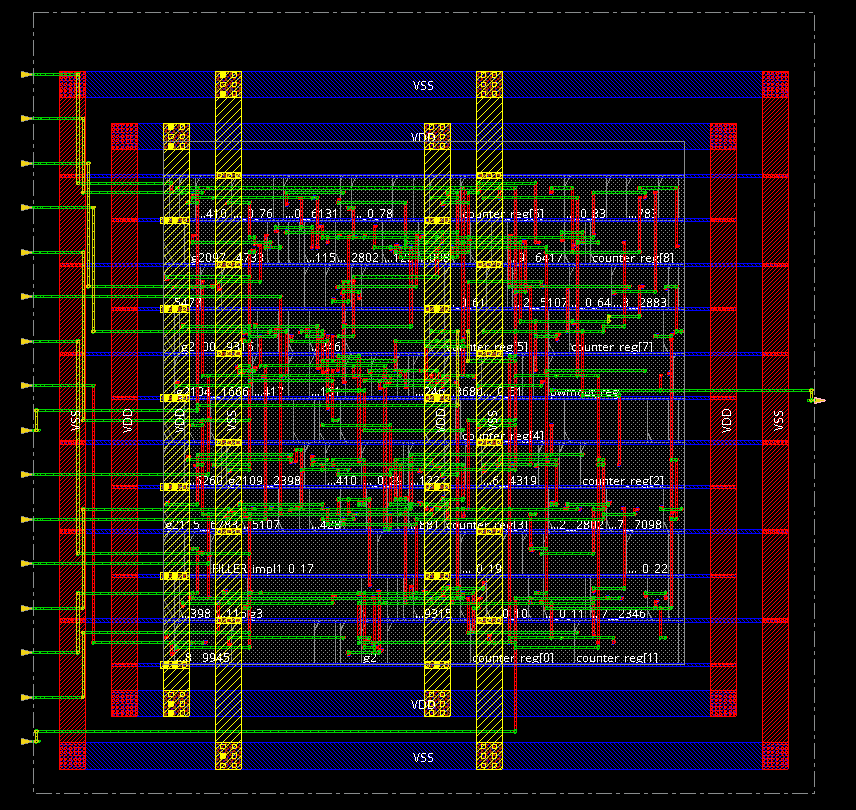

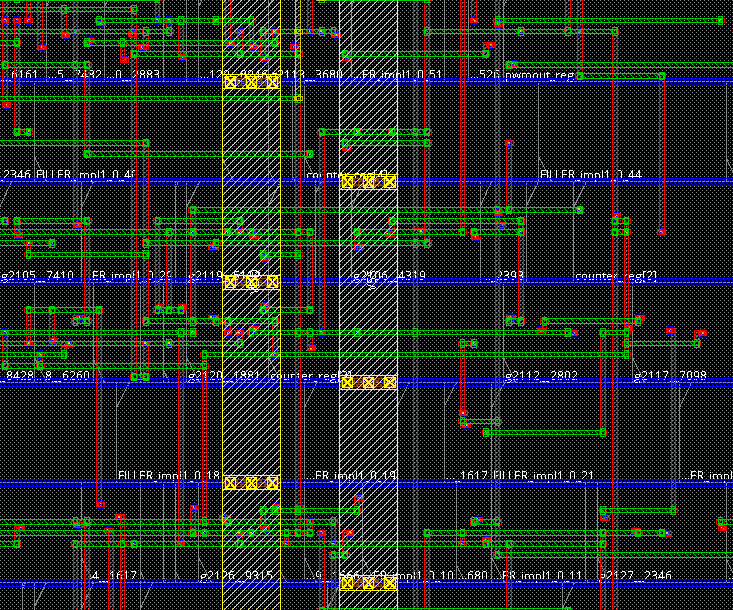

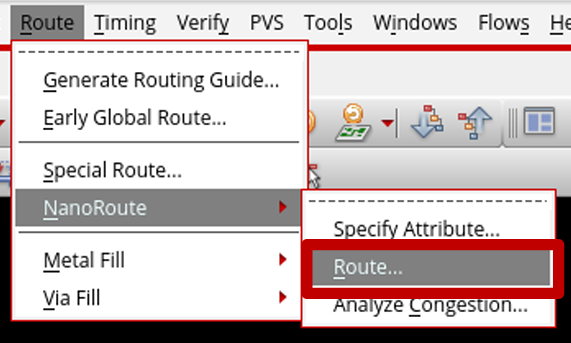

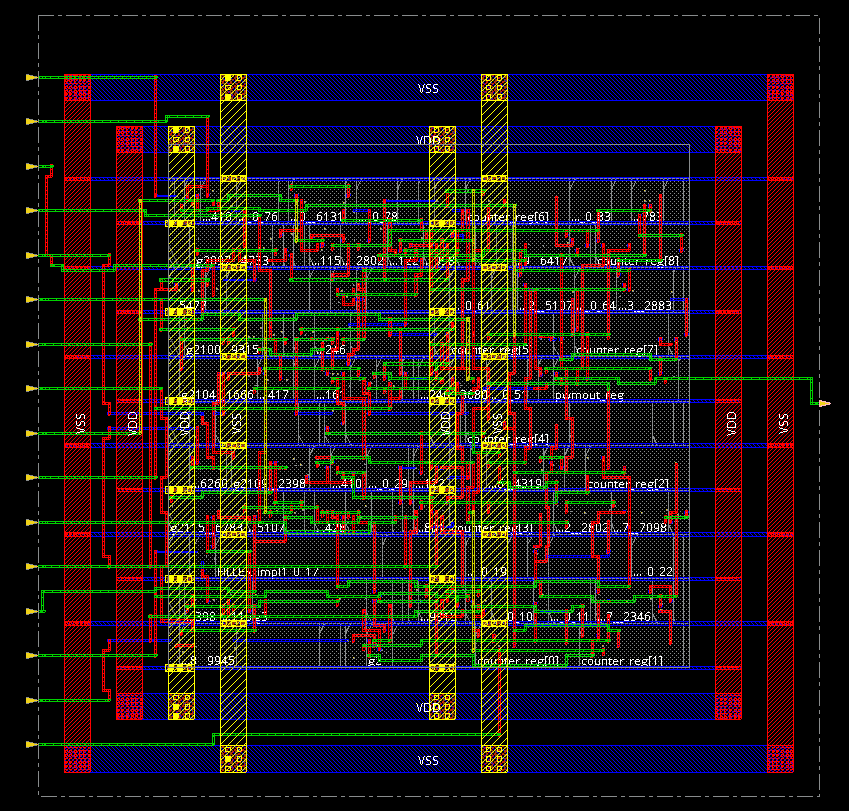

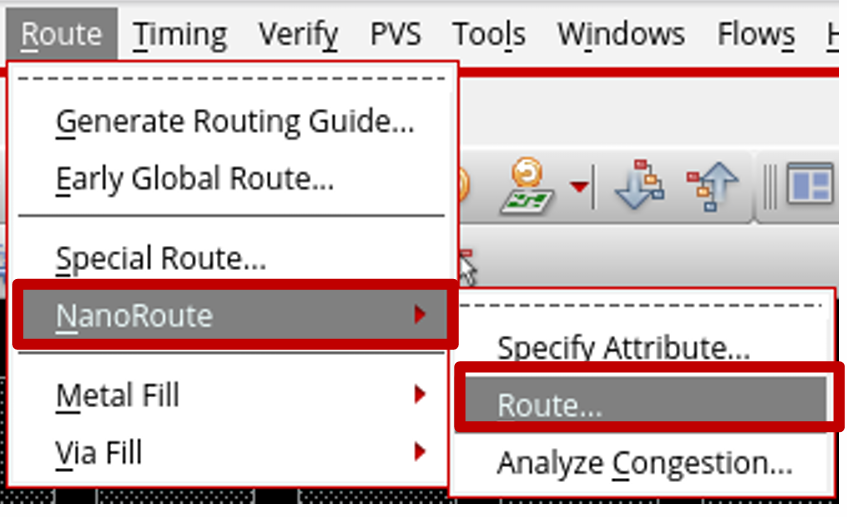

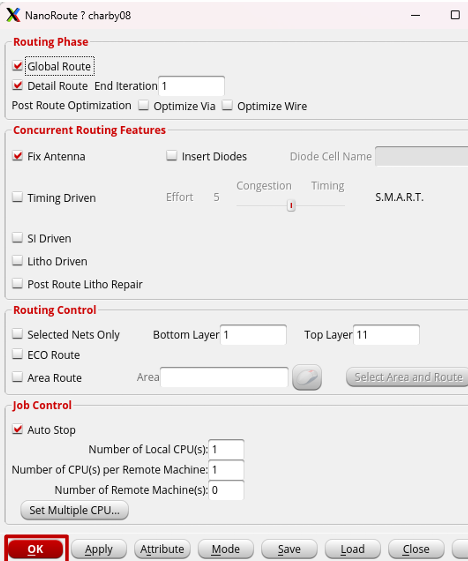

P&R: Routing

P&R: Routing

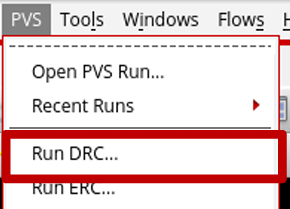

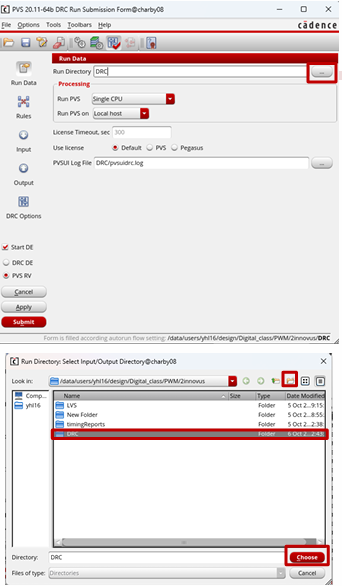

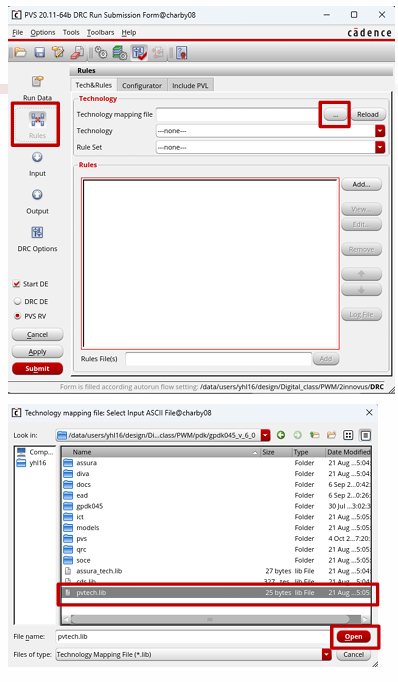

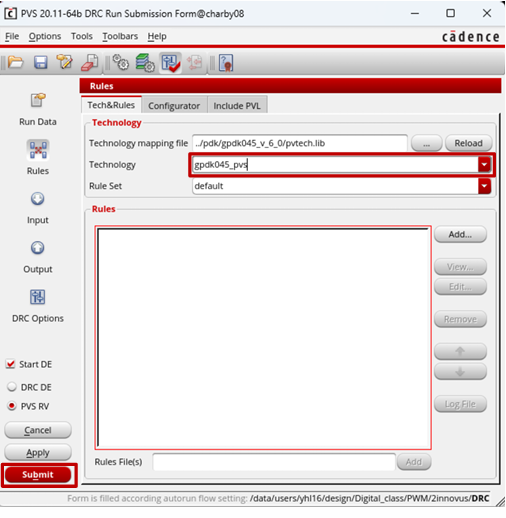

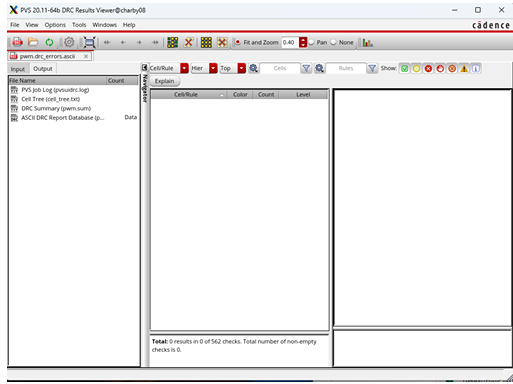

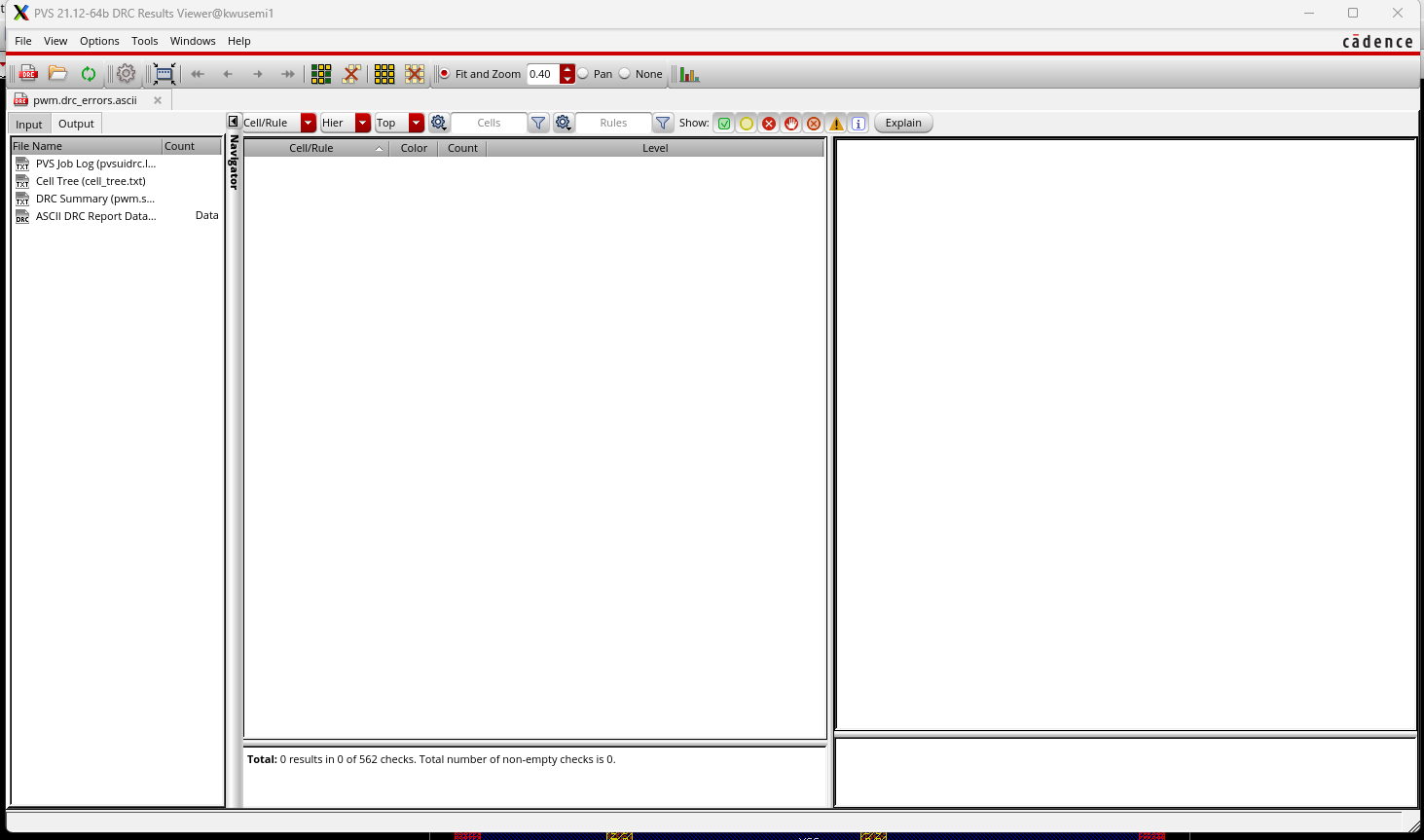

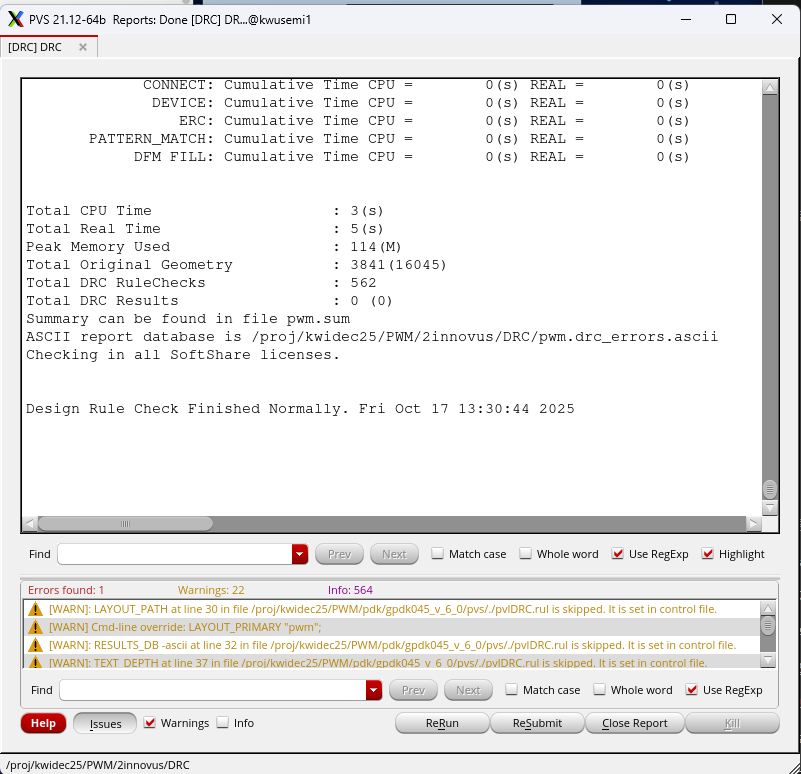

P&R: Check DRC

PVS 설정

DRC Run

DRC Metal 간격

• 임의로DRC 에러생성

DRC result

DRC result

• Error 가 있을 경우 위와 같이 메시지 표시

• 더블 클릭 시 해당 위치 하이라이트 표시

• Error를 고치기 위해서는 Size 또는 해당 부분만 옮겨서 DRC 문제 해결

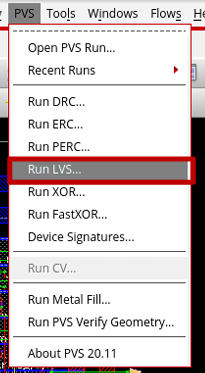

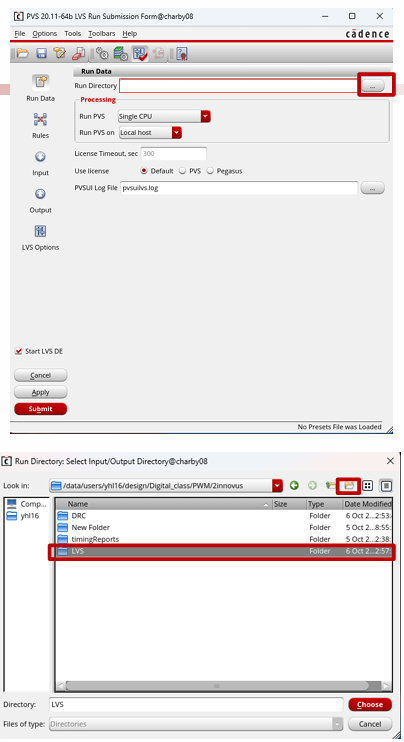

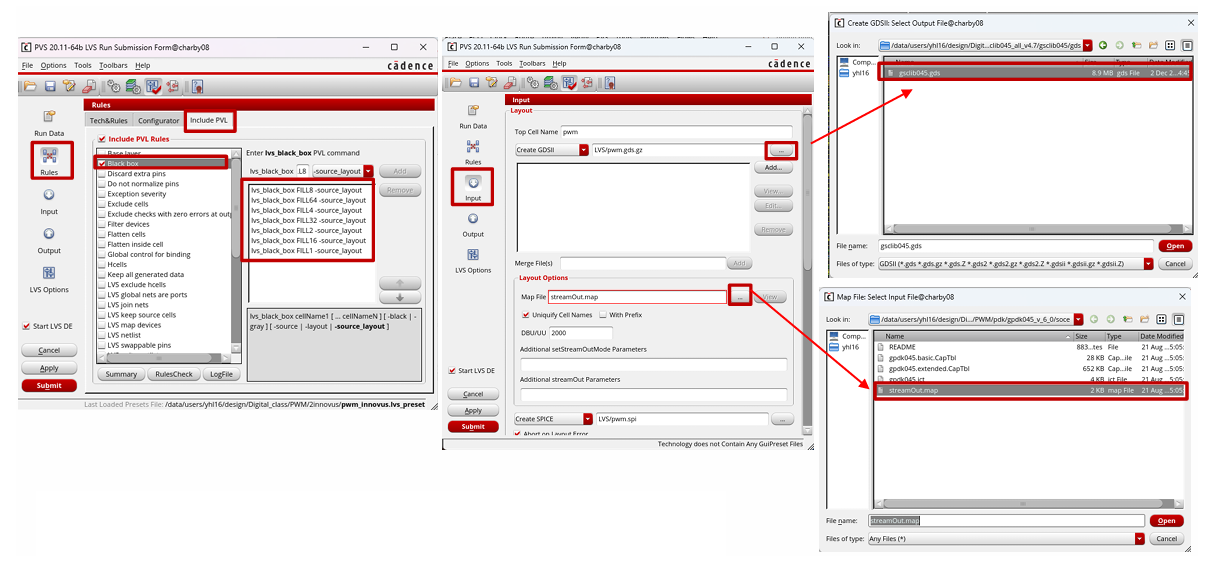

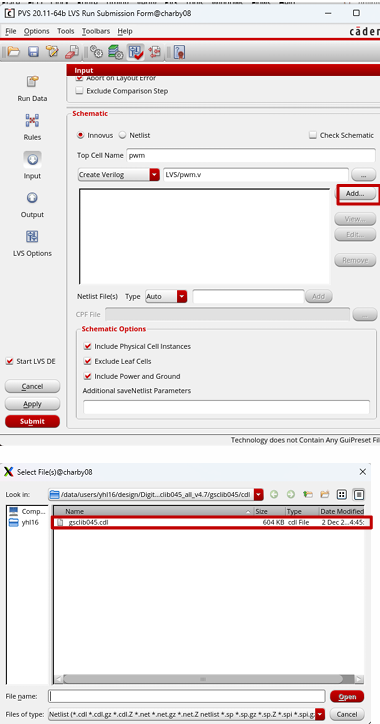

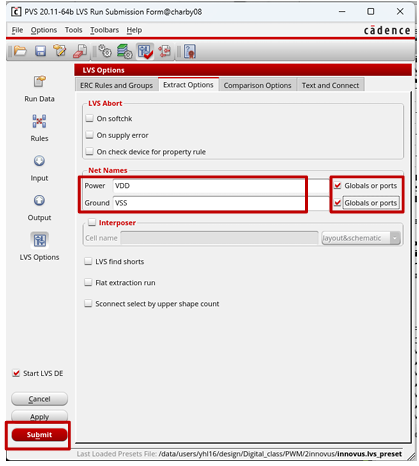

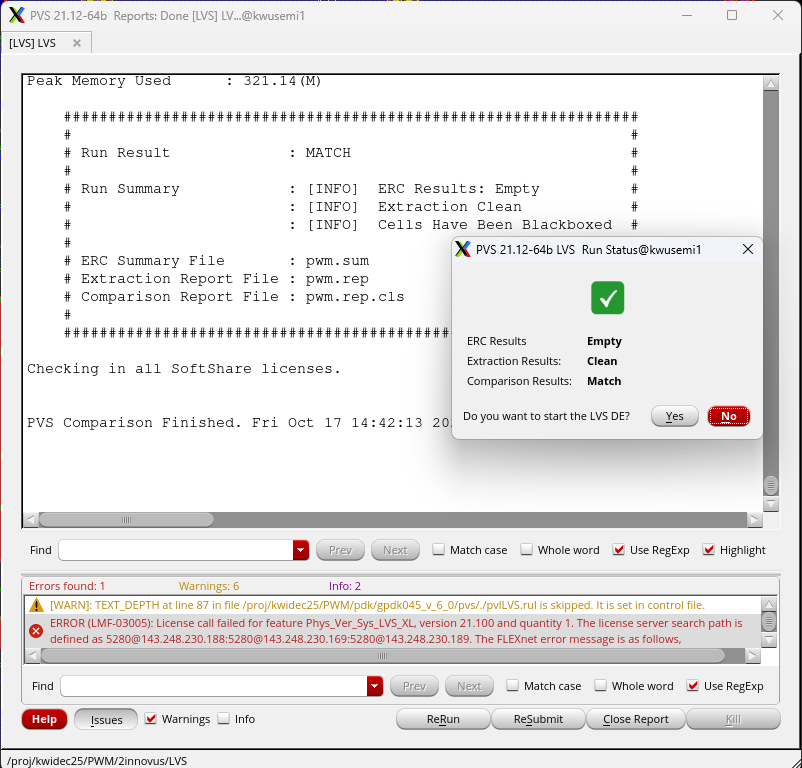

P&R: Check LVS

PVS 설정

Black Box 설정

Power Net 설정

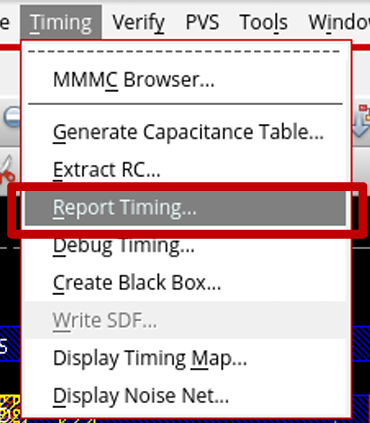

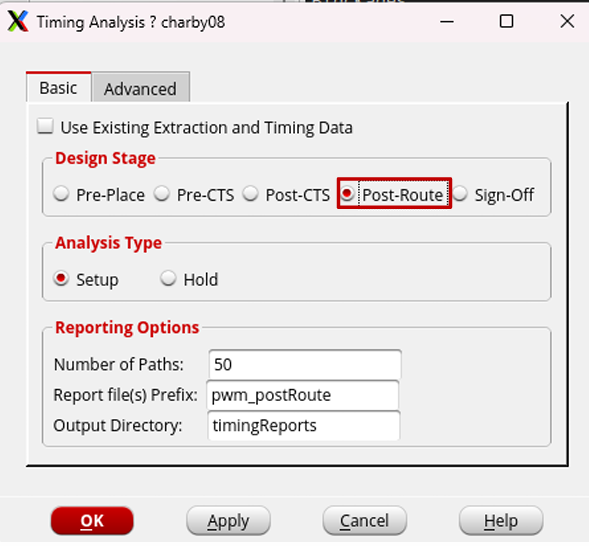

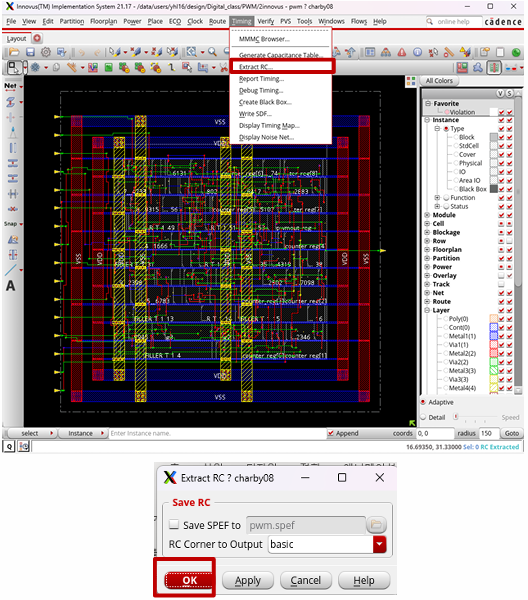

P&R: Timing Report 확인

Time Report 추출

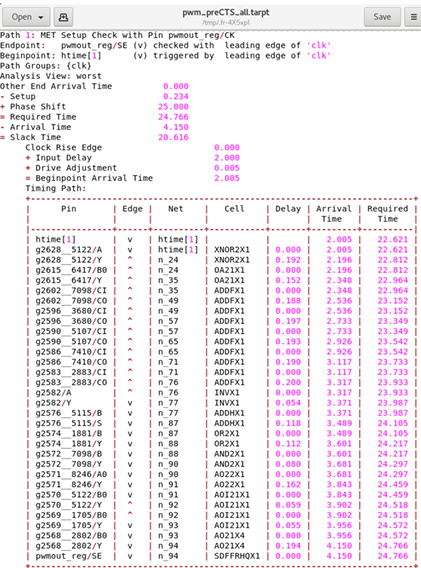

Report분석

• 파일위치

• ./ pwm/2innovus/timingReports/pwm_preCTS_all.tarpt

• Begin point: 경로의 시작점

• End point: 경로의 종료점

• Path Group: 경로의 분류

• Analysis View: 분석 환경

• Slack: 타이밍 여유(Required Time -Arrival Time)

• Timing Path: 실제 신호가 거치는 셀 / 넷 / 핀의 리스트와 각 단계 별 propagation delay

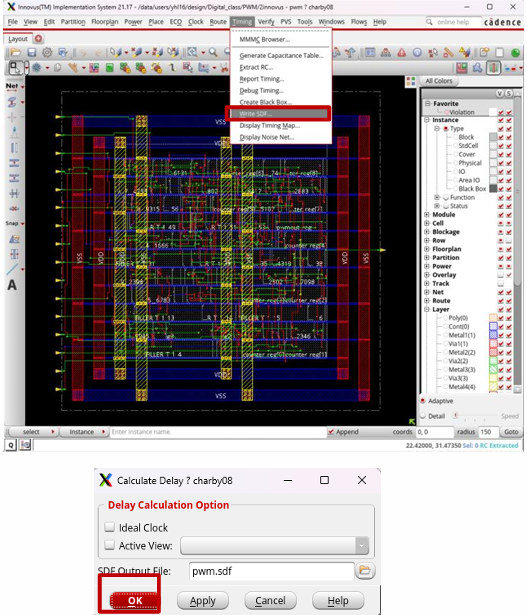

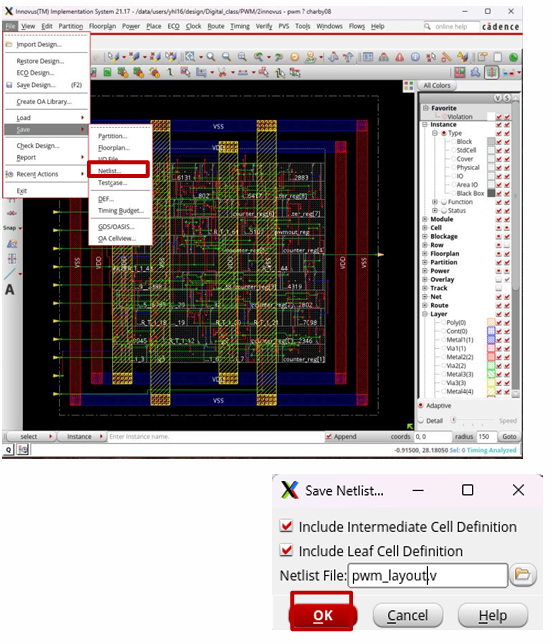

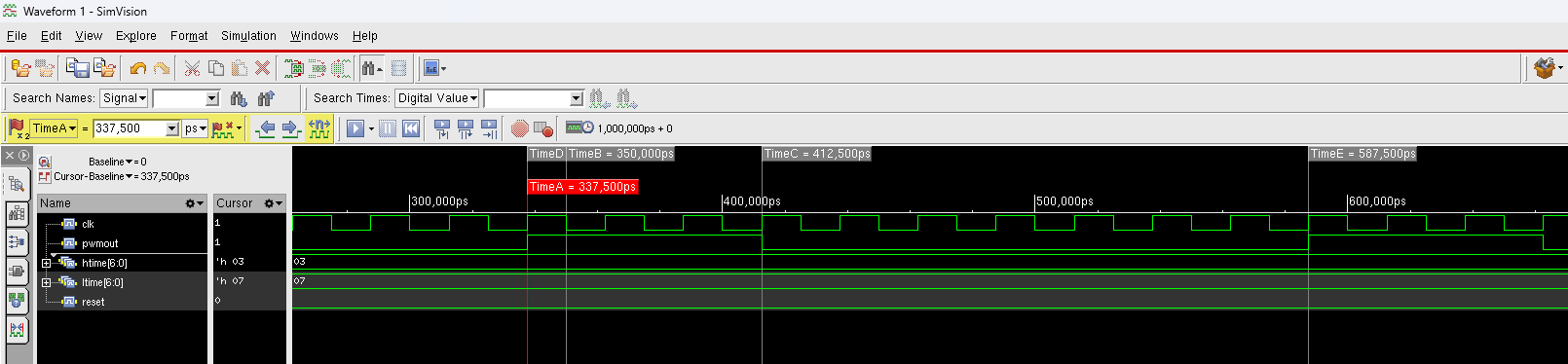

P&R: Post Layout Simulation

SDF & Netlist 추출

Simulation Setting

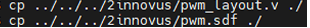

• cd ../1genus/ rtl 폴더로이동 • Innovus에서추출한netlist, sdf파일을PLS 폴더로 이동

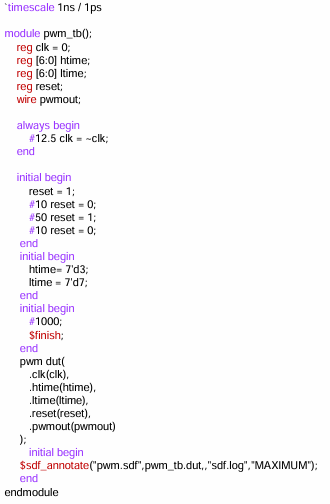

Test bench 작성

• PLS 폴더에작성

Netlist 수정

- 1genus/ filelist → pwm_layout.v HiCSL 로수정

Xcelium 실행

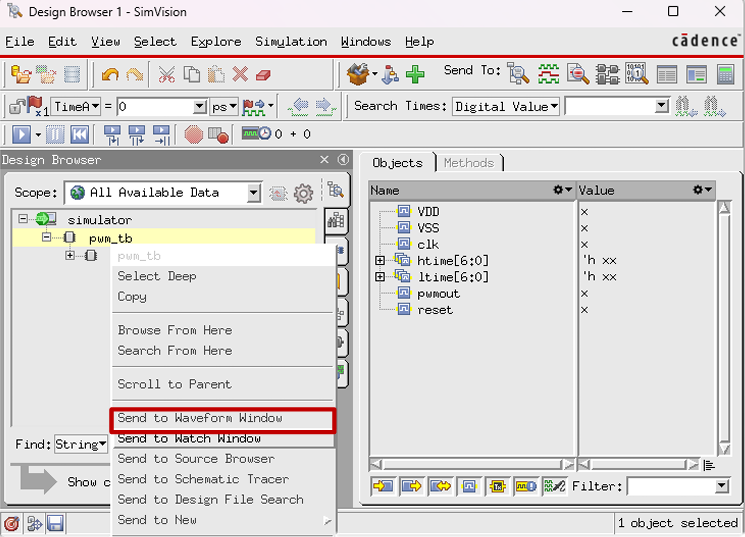

Waveform window 띄우기

Simulation 실행

P&R: Top Verilog 작성

module top_pwm (clk, reset, htime, ltime, pwmout,VDD, VSS);

input clk;

input reset;

input [6:0] htime, ltime;

input VDD;

input VSS;

output pwmout;

PADI_ESD_Metal9 pad_clk (.PAD(clk));

PADI_ESD_Metal9 pad_reset (.PAD(reset));

PADI_ESD_Metal9 pad_htime0 (.PAD(htime[0]));

PADI_ESD_Metal9 pad_htime1 (.PAD(htime[1]));

PADI_ESD_Metal9 pad_htime2 (.PAD(htime[2]));

PADI_ESD_Metal9 pad_htime3 (.PAD(htime[3]));

PADI_ESD_Metal9 pad_htime4 (.PAD(htime[4]));

PADI_ESD_Metal9 pad_htime5 (.PAD(htime[5]));

PADI_ESD_Metal9 pad_htime6 (.PAD(htime[6]));

PADI_ESD_Metal9 pad_ltime0 (.PAD(ltime[0]));

PADI_ESD_Metal9 pad_ltime1 (.PAD(ltime[1]));

PADI_ESD_Metal9 pad_ltime2 (.PAD(ltime[2]));

PADI_ESD_Metal9 pad_ltime3 (.PAD(ltime[3]));

PADI_ESD_Metal9 pad_ltime4 (.PAD(ltime[4]));

PADI_ESD_Metal9 pad_ltime5 (.PAD(ltime[5]));

PADI_ESD_Metal9 pad_ltime6 (.PAD(ltime[6])); PADO_ESD_Metal9 pad_pwmout (.PAD(pwmout));

PVDD_Metal9 pad_vdd(.VDD(VDD));

PVSS_Metal9 pad_vss(.VSS(VSS));

PCORNER_TL_Metal9 corner_TL();

PCORNER_TR_Metal9 corner_TR();

PCORNER_BL_Metal9 corner_BL();

PCORNER_BR_Metal9 corner_BR();

pwm pwm1(

.clk(clk),

.reset(reset),

.htime(htime),

.ltime(ltime),

.pwmout(pwmout)

);

endmoduleTop 작성

• Pad 포함해서작성

• ../1genus/ outputs_pwm/top_pwm_syn.v 저장

P&R: Top Innovus 설정

Innouvs세팅

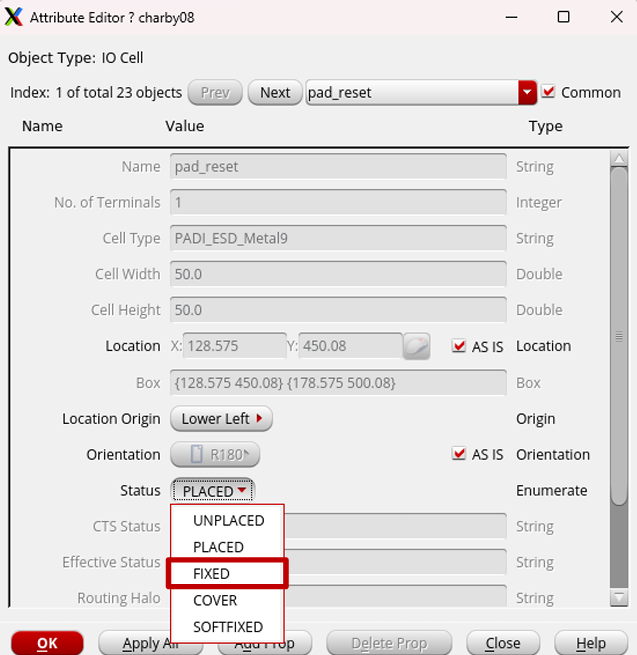

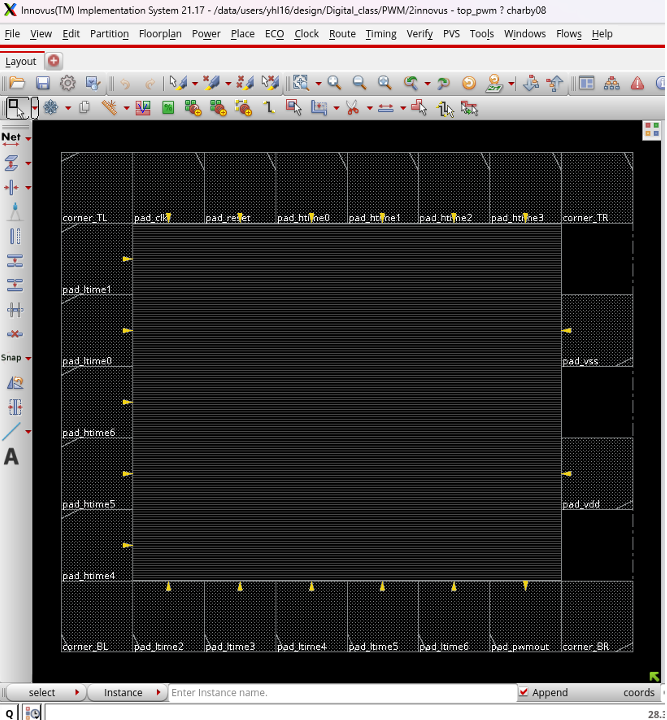

P&R: Top Flooorplan

Floorplan

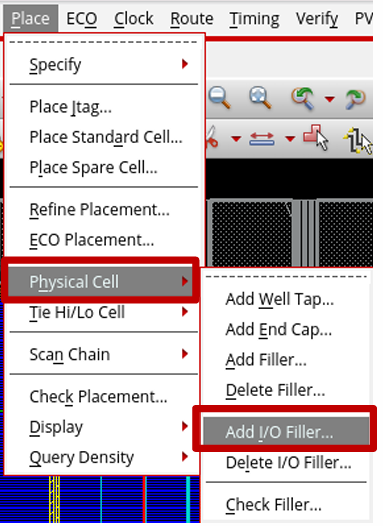

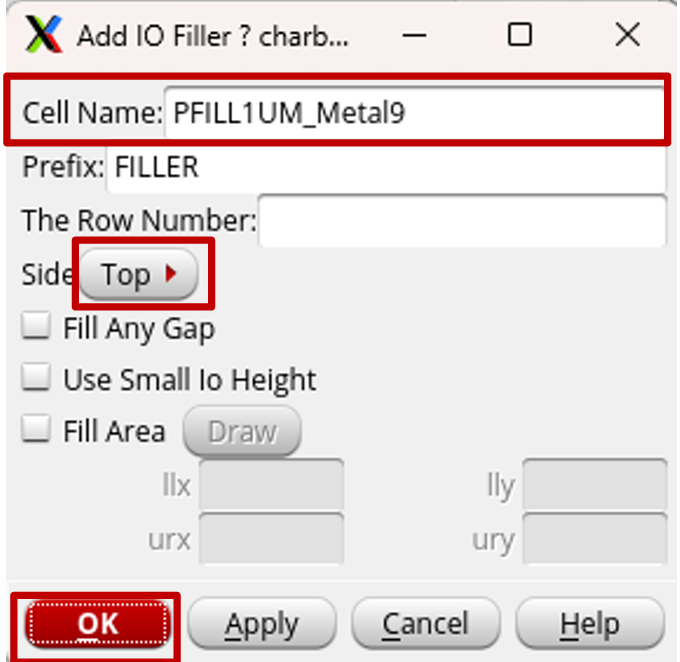

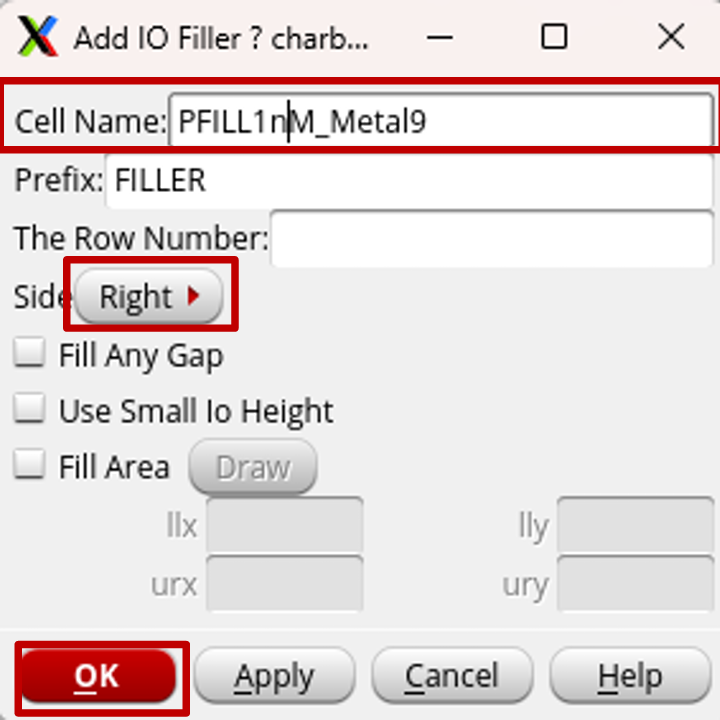

P&R: Top IO Filler

IO Filler 추가

Power Stripe 추가

Cell 을위한Power line 추가

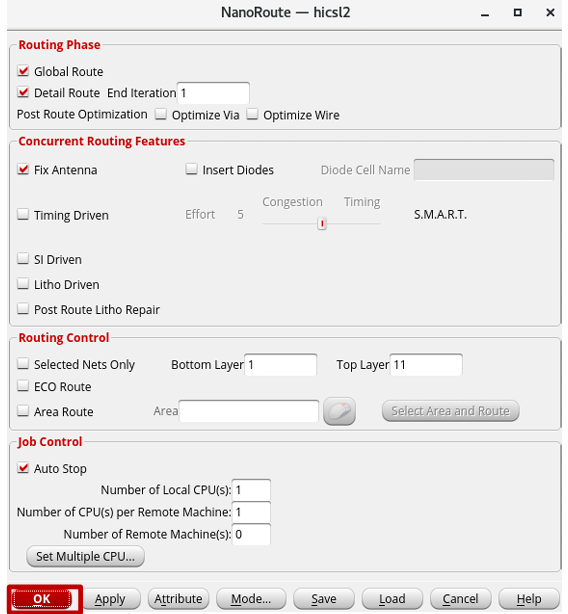

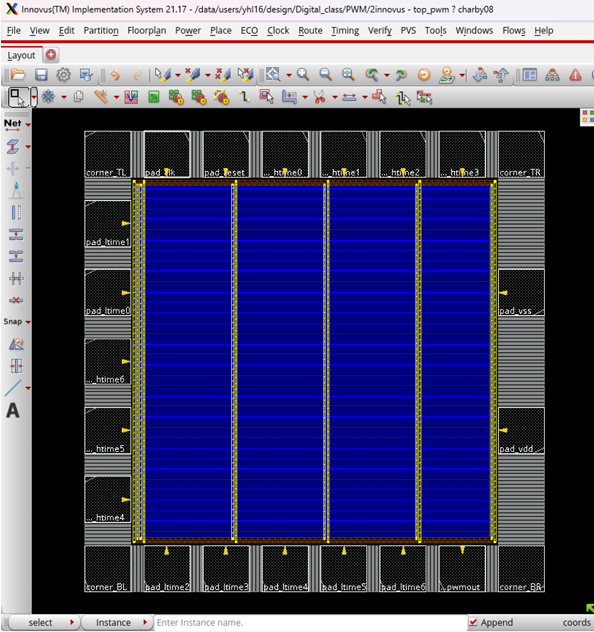

P&R: TopCell 배치

Standard cell 배치

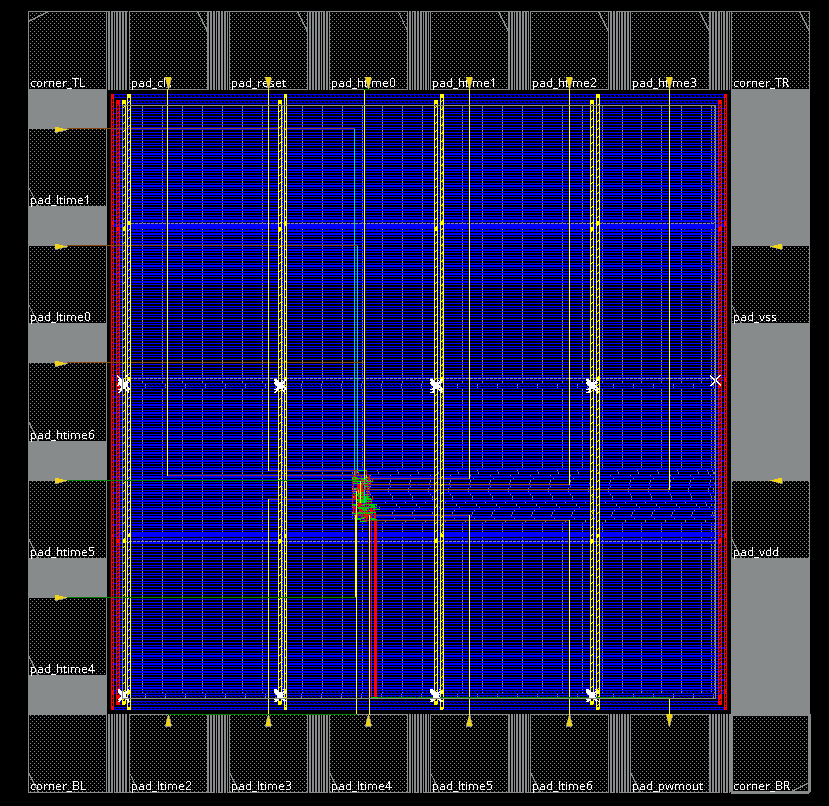

Routing

Top Cell

결론

이번에 들은 디지털 집적회로 기초 설계 실습은 Verilog를 이용해 실제 IC 설계 과정을 처음부터 끝까지 경험해보는 수업이었습니다.

PWM 회로를 직접 설계하면서 Vivado로 RTL 코드를 작성하고 시뮬레이션을 통해 동작을 검증했습니다. 이후에는 Cadence의 Genus로 논리 합성(Synthesis)을 진행해, RTL 코드가 게이트 레벨 회로로 바뀌는 과정을 직접 확인했습니다.

그 다음 Innovus를 사용해서 Place & Route 단계까지 수행하면서, 회로를 실제 실리콘 위에 배치하고 배선하는 과정도 실습했어요. 마지막에는 **Post Layout Simulation(PLS)**을 통해 합성 전후의 지연 차이를 비교하며, 물리적 설계가 회로 동작에 미치는 영향을 배웠습니다.

이 과정을 통해 단순히 코드를 짜는 것뿐 아니라, 하드웨어 설계가 실제 칩으로 구현되기까지의 전체 흐름을 이해할 수 있었고, 각 툴의 역할과 설계 데이터의 연결 구조를 명확히 배울 수 있었습니다.

무엇보다 FPGA 수준이 아니라 ASIC 수준의 설계 절차를 직접 경험해본 게 큰 도움이 되었습니다.

'IEDC' 카테고리의 다른 글

| [디지털 집적회로 기초 설계 실습]_RTL부터 P&R 까지 통합 플로우_1 (0) | 2025.10.17 |

|---|