목적

- 디지털 시스템 설계에서 다운 카운터의 동작을 구현하고 테스트

기본 구성

- 4개의 .T_FF : 4비트 값을 기억

- clk : 값이 변하는 시점 지성( 상승엣지 기준)

- reset : 상태를 0000으로 초기화

- enable : 카운팅을 제어하는 신호 (1일 때만 카운트)

사용 코드_ T_FF

module T_flip_flop_p(

input clk, reset_p,

input t,

output reg q);

always @(posedge clk, posedge reset_p)begin

if(reset_p) q = 0;

else if(t) q = ~q;

else q = q;

end

endmodule

사용 코드_1

module up_counter_asyc (

input clk, // 외부에서 주어지는 기본 클럭 입력

input reset_p, // 비동기 리셋 입력 (양의 엣지에서 동작한다고 가정)

output [3:0] count // 4비트 카운터 출력 (0000 ~ 1111)

);

// 첫 번째 T 플립플롭: 가장 하위 비트 (LSB)

// 외부 clk를 직접 입력으로 받아 토글 (T=1, 항상 토글)

// count[0]은 1클럭마다 0↔1 전환 (1Hz 기준)

T_flip_flop_n T0(

.clk(clk), // 외부 클럭 입력

.reset_p(reset_p), // 비동기 리셋

.t(1), // T 입력은 항상 1 (토글 모드)

.q(count[0]) // 출력은 count[0]

);

// 두 번째 T 플립플롭: 두 번째 비트

// 이전 출력(count[0])을 클럭으로 사용 → 비동기 구조

// count[0]이 토글될 때마다 이 플립플롭도 토글

T_flip_flop_n T1(

.clk(count[0]), // 이전 비트 출력이 클럭 역할

.reset_p(reset_p),

.t(1),

.q(count[1])

);

// 세 번째 T 플립플롭

// count[1]이 토글될 때마다 이 플립플롭이 토글

T_flip_flop_n T2(

.clk(count[1]),

.reset_p(reset_p),

.t(1),

.q(count[2])

);

// 네 번째 T 플립플롭: 가장 상위 비트 (MSB)

// count[2]의 토글에 따라 토글

T_flip_flop_n T3(

.clk(count[2]),

.reset_p(reset_p),

.t(1),

.q(count[3])

);

endmodule

사용 코드_2

module up_counter_p(

input clk, // 클럭 입력

input reset_p, // 비동기 리셋 입력 (posedge에서 작동)

input enable, // enable 신호 (1일 때만 카운팅)

output reg [3:0] count // 4비트 카운터 출력

);

always @(posedge clk, posedge reset_p) begin

if (reset_p)

count = 0; // 리셋 시 카운터를 0으로 초기화

else if (enable)

count = count + 1; // enable이 1일 때마다 1씩 감소 (다운 카운트)

end

endmodule

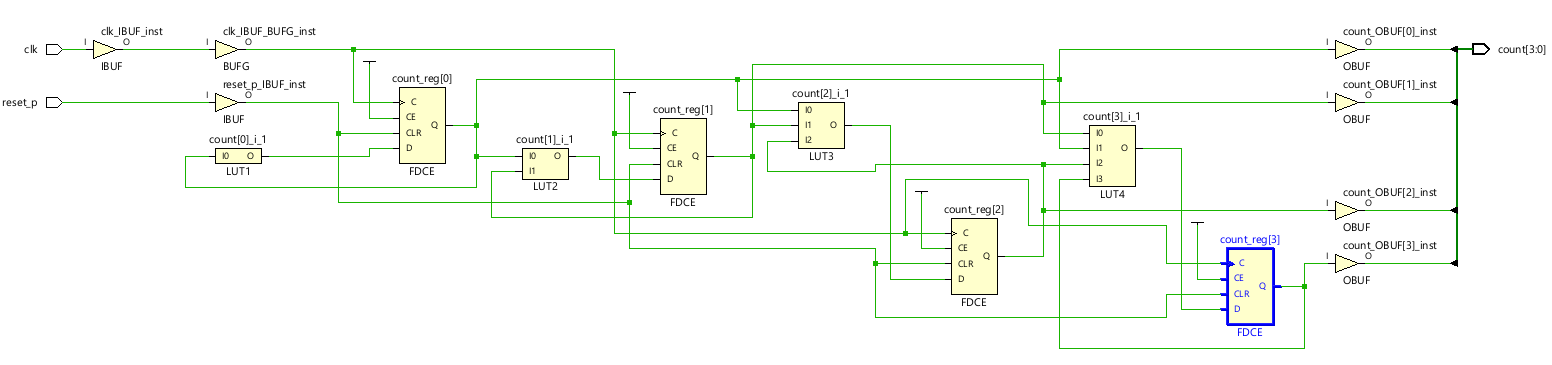

Schematic

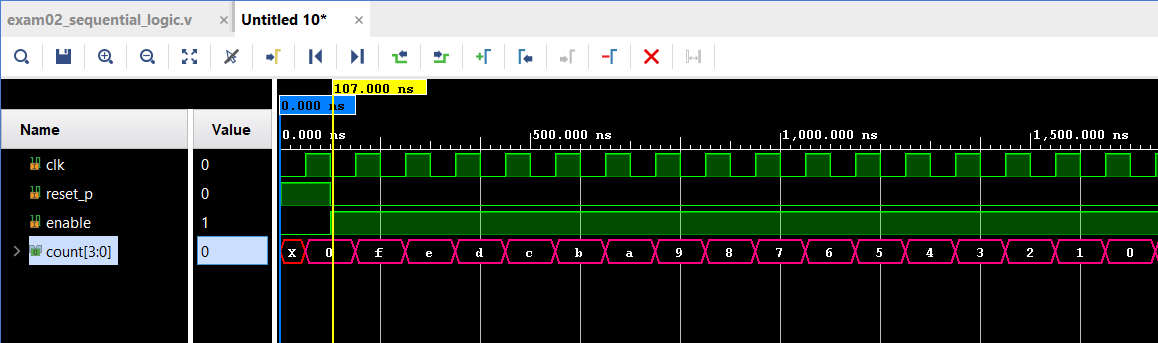

Simulation

결과

- 이 회로는 enable 신호가 있을 때 클럭 상승 엣지마다 1씩 증가하는 Up counter이다.

- 비동기 리셋 신호를 통해 언제든지 출력을 초기화 할 수 있습니다.

- 디지털 순차회로의 기본 구성요소로서 다양한 실습과 시스템에 적용될 수 있다.

'Verilog_RTL 설계 > Basys_3' 카테고리의 다른 글

| [Basys_3] Implementation of a 7-Segment Counter Circuit with Debouncing and Edge Detection (0) | 2025.07.07 |

|---|---|

| [Sequential Circuit] Ring_Counter (0) | 2025.07.07 |

| [Sequential Circuit] Down_Counter (0) | 2025.07.07 |

| [Sequential Circuit] D_FF (0) | 2025.07.07 |

| [Basys 3_Vivado] Basys 3 실행 방법 (0) | 2025.07.03 |